Rainbow Electronics W90N740 User Manual

Page 85

W90N740

Publication Release Date: November 26, 2004

- 81 -

Revision A4

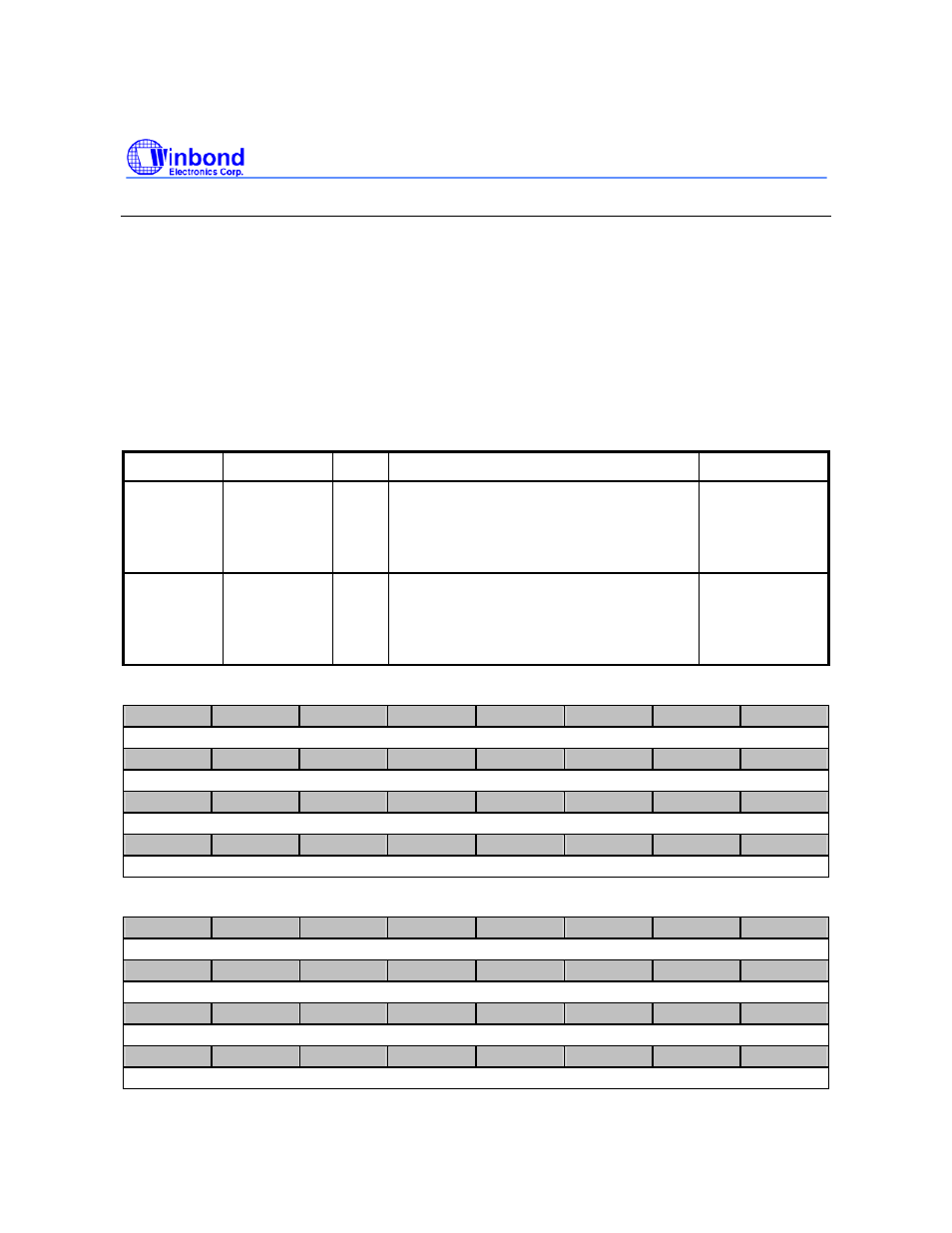

CAM Address Registers (CAMxx_0, CAMxx_1)

There are 16 entries for the Destination Address (entries 0~12) and the Pause Control Packet (entries

13~15). For the destination address values, one destination address consists of 6 bytes with 2-word

access port.

To send a Pause Control Packet, write in the register set {CAM13M, CAM13L} with the destination

address, the {CAM14M, CAM14L} entry with the source address, and the {CAM15M, CAM15L} entry

with length/type, op-code, and operand, then set the SDPZ bit in the MCMDR (MAC Command

Register).

The CPU uses the CAM address register as a database for destination address. To activate the CAM

function, the appropriate enable bit has to be set in the CAMEN register.

Register Address R/W

Description

Reset

Value

CAM0M_0

CAM0L_0

l

CAM15M_0

CAM15L_0

0xFFF0.3008

0xFFF0.300C

l

0xFFF0.3080

0xFFF0.3084

R/W

CAM0 Most Significant Word Register

CAM0 Least Significant Word Register

l

CAM15 Most Significant Word Register

CAM15 Least Significant Word Register

0x0000.0000

0x0000.0000

l

0x0000.0000

0x0000.0000

CAM0M_1

CAM0L_1

l

CAM15M_1

CAM15L_1

0xFFF0.3808

0xFFF0.380C

l

0xFFF0.3880

0xFFF0.3884

R/W

CAM0 Most Significant Word Register

CAM0 Least Significant Word Register

l

CAM15 Most Significant Word Register

CAM15 Least Significant Word Register

0x0000.0000

0x0000.0000

l

0x0000.0000

0x0000.0000

CAMxM (CAM15M excluded)

31

30

29

28

27

26

25

24

Destination Address Byte 6 (Most Significant Byte)

23

22

21

20

19

18

17

16

Destination Address Byte 5

15

14

13

12

11

10

9

8

Destination Address Byte 4

7

6

5

4

3

2

1

0

Destination Address Byte 3

CAMxL (CAM15L excluded)

31

30

29

28

27

26

25

24

Destination Address Byte 2

23

22

21

20

19

18

17

16

Destination Address Byte 1

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

Reserved