Rainbow Electronics W90N740 User Manual

Page 87

W90N740

Publication Release Date: November 26, 2004

- 83 -

Revision A4

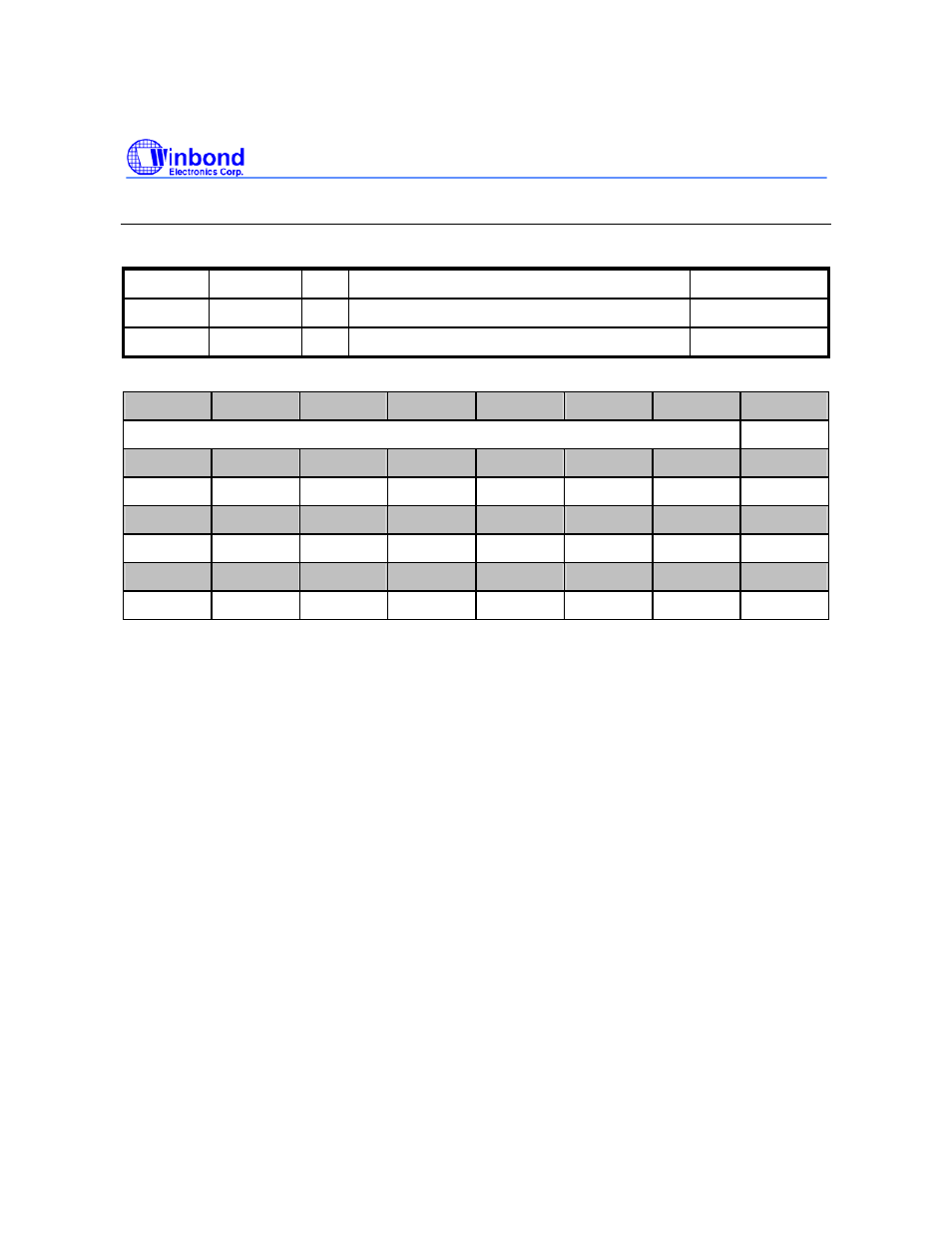

MAC Interrupt Enable Register (MIEN_0, MIEN_1)

Register Address R/W

Description

Reset

Value

MIEN_1

0xFFF0.3088

R/W MAC Interrupt Enable Register

0x0000.0000

MIEN_2

0xFFF0.3888

R/W MAC Interrupt Enable Register

0x0000.0000

31

30

29

28

27

26

25

24

Reserved

EnTxBErr

23

22

21

20

19

18

17

16

EnTDU EnLC

EnTXABT

EnNCS

EnEXDEF

EnTXCP

EnTXEMP

EnTXINTR

15

14

13

12

11

10

9

8

Reserved

EnCFR EnNATErr

EnNATOK

EnRxBErr

EnRDU

EnDEN EnDFO

7

6

5

4

3

2

1

0

EnMMP EnRP EnALIE

EnRXGD

EnPTLE

EnRXOV

EnCRCE

EnRXINTR

EnTxBErr [24]: Enable Transmit Bus ERROR interrupt

Default value: 0

Set this bit to enable the interrupt, which is generated if system bus access error from Tx to system

memory occurred. If the interrupt is triggered, the Tx state machine will stay at Halt state. The software

reset is recommended while this interrupt occurred.

EnTDU [23]: Enable Transmit Descriptor Unavailable interrupt

Default value: 0

Set this bit to enable the interrupt, which is generated if transmit descriptors owned to the TxDMA is

unavailable. That means, if the TxDMA finds the ownership of descriptors is not belonged to TxDMA, it

will generate an interrupt and Tx operation will be ceased till the user issues a write command to

Transmit Start Demand register to restart Tx operation.

EnLC [22]: Enable Late Collision interrupt

Default value: 0

Set this bit to enable the interrupt, which is generated if a collision occurs after 512 bit times.

EnTXABT [21]: Enable Transmit Abort interrupt

Default value: 0