Rainbow Electronics W90N740 User Manual

Page 168

W90N740

- 164 -

TERI [2]: Tailing Edge of RI#

This bit is set whenever RI# input has changed from high to low, and it will be reset if the CPU reads the

MSR.

DDSR [1]: DSR# State Change

This bit is set whenever DSR# input has changed state, and it will be reset if the CPU reads the MSR.

DCTS [0]: CTS# State Change

This bit is set whenever CTS# input has changed state, and it will be reset if the CPU reads the MSR.

Whenever any of MSR [3:0] is set to logic 1, a Modem Status Interrupt is generated if IER[3]=1. Writing

MSR is a null operation (not suggested).

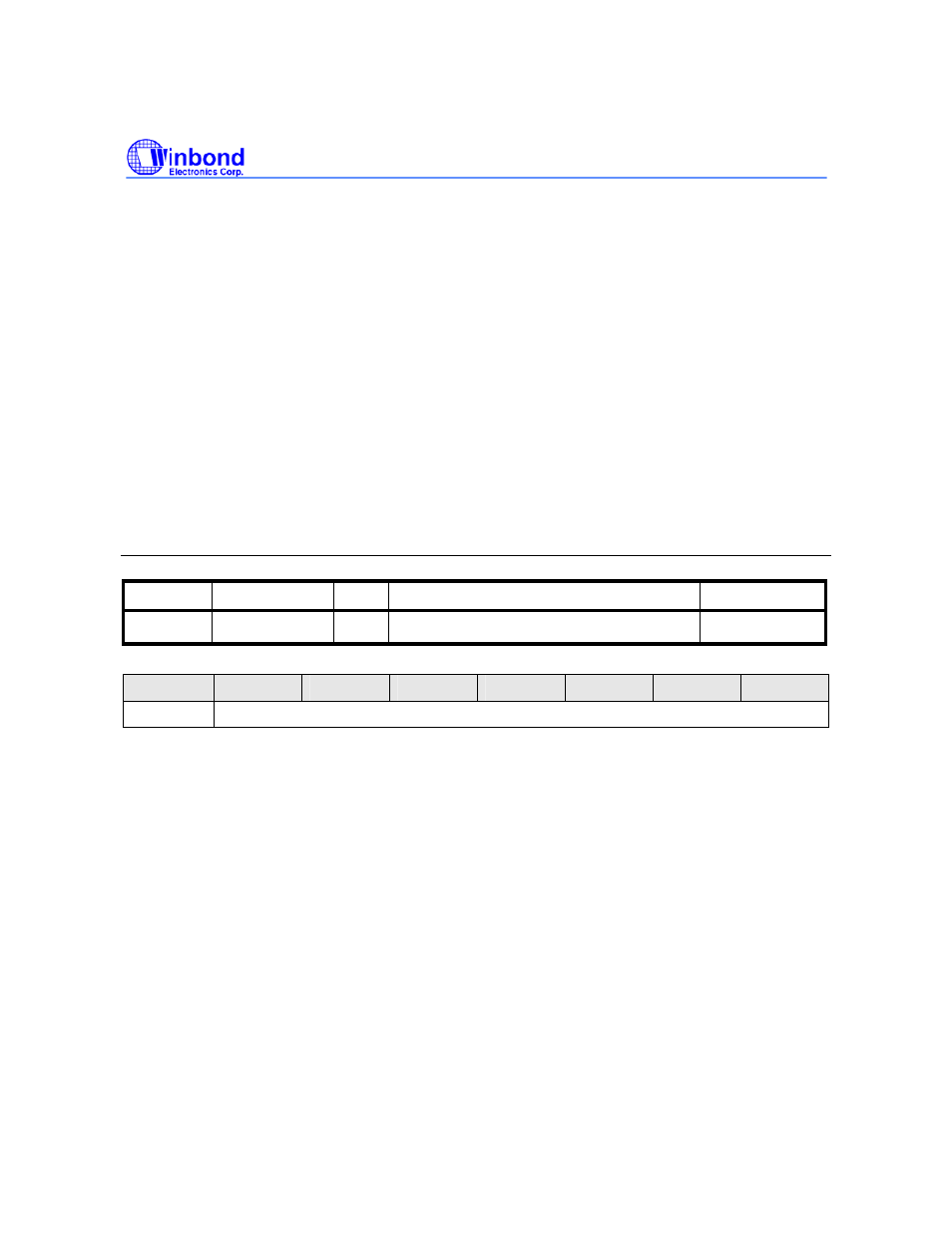

Time Out Register (TOR)

Register Address R/W

Description

Reset

Value

TOR

0xFFF8.001C R/W Time Out Register

0x0000.0000

7

6

5

4

3

2

1

0

TOIE TOIC

TOIE [7]: Time Out Interrupt Enable

The feature of receiver time out interrupt is enabled only when TOR [7] = IER[0] = 1.

TOIC [6:0]: Time Out Interrupt Comparator

The time out counter resets and starts counting (the counting clock = baud rate) whenever the RX FIFO

receives a new data word. Once the content of time out counter (TOUT_CNT) is equal to that of time out

interrupt comparator (TOIC), a receiver time out interrupt (Irpt_TOUT) is generated if TOR [7] = IER [0] =

1. A new incoming data word or RX FIFO empty clears Irpt_TOUT.