Rainbow Electronics W90N740 User Manual

Page 133

W90N740

Publication Release Date: November 26, 2004

- 129 -

Revision A4

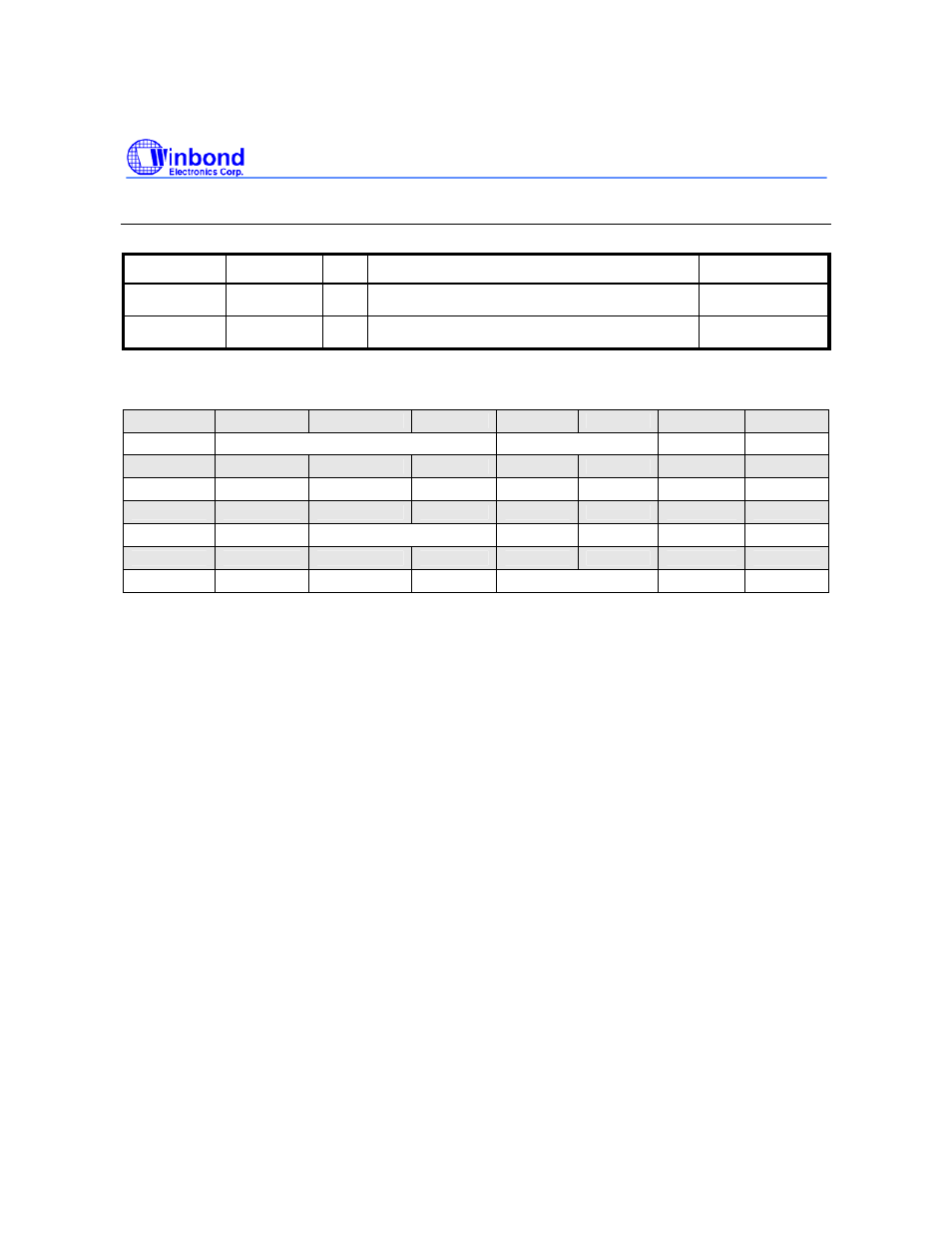

Channel 0/1 Control Register (GDMA_CTL0, GDMA_CTL1)

Register Address

R/W

Description

Reset

Value

GDMA_CTL0 0xFFF0.4000 R/W

Channel 0 Control Register

0x0000.0000

GDMA_CTL1 0xFFF0.4020 R/W

Channel 1 Control Register

0x0000.0000

TC_WIDTH [30:28]: nRTC/nWTC active width selection, from 1 to 7 HCLK cycles.

REQ_SEL [27:26]: External request pin selection, if GDMAMS [3:2]=00, REQ_SEL doesn’t care.

If REQ_SEL [27:26]=00, external request doesn’t use.

If REQ_SEL [27:26]=01, use nXDREQ1.

If REQ_SEL [27:26]=10, use nXDREQ2.

If REQ_SEL [27:26]=11, use nXDREQ3.

REQ_ATV [25]: nXDREQ High/Low active selection

If REQ_ATV [25]=0, nXDREQ1/2/3 is LOW active.

If REQ_ATV [25]=1, nXDREQ1/2/3 is HIGH active.

ACK_ATV [24]: nXDACK High/Low active selection

If ACK_ATV [24]=0, nXDACK is LOW active.

If ACK_ATV [24]=1, nXDACK is HIGH active.

31

30

29

28

27

26

25

24

RESERVED

TC_WIDTH REQ_SEL

REQ_ATV

ACK_ATV

23

22

21

20

19

18

17

16

RW_TC SABNDERR

DABNDERR

GDMAERR

AUTOIEN

TC

BLOCK SOFTREQ

15

14

13

12

11

10

9

8

DM

RESERVED

TWS SBMS

RESERVED

BME SIEN

7

6

5

4

3

2

1

0

SAFIX DAFIX SADIR DADIR

GDMAMS RESERVED

GDMAEN