Pin description – Rainbow Electronics W90N740 User Manual

Page 14

W90N740

- 10 -

6. PIN DESCRIPTION

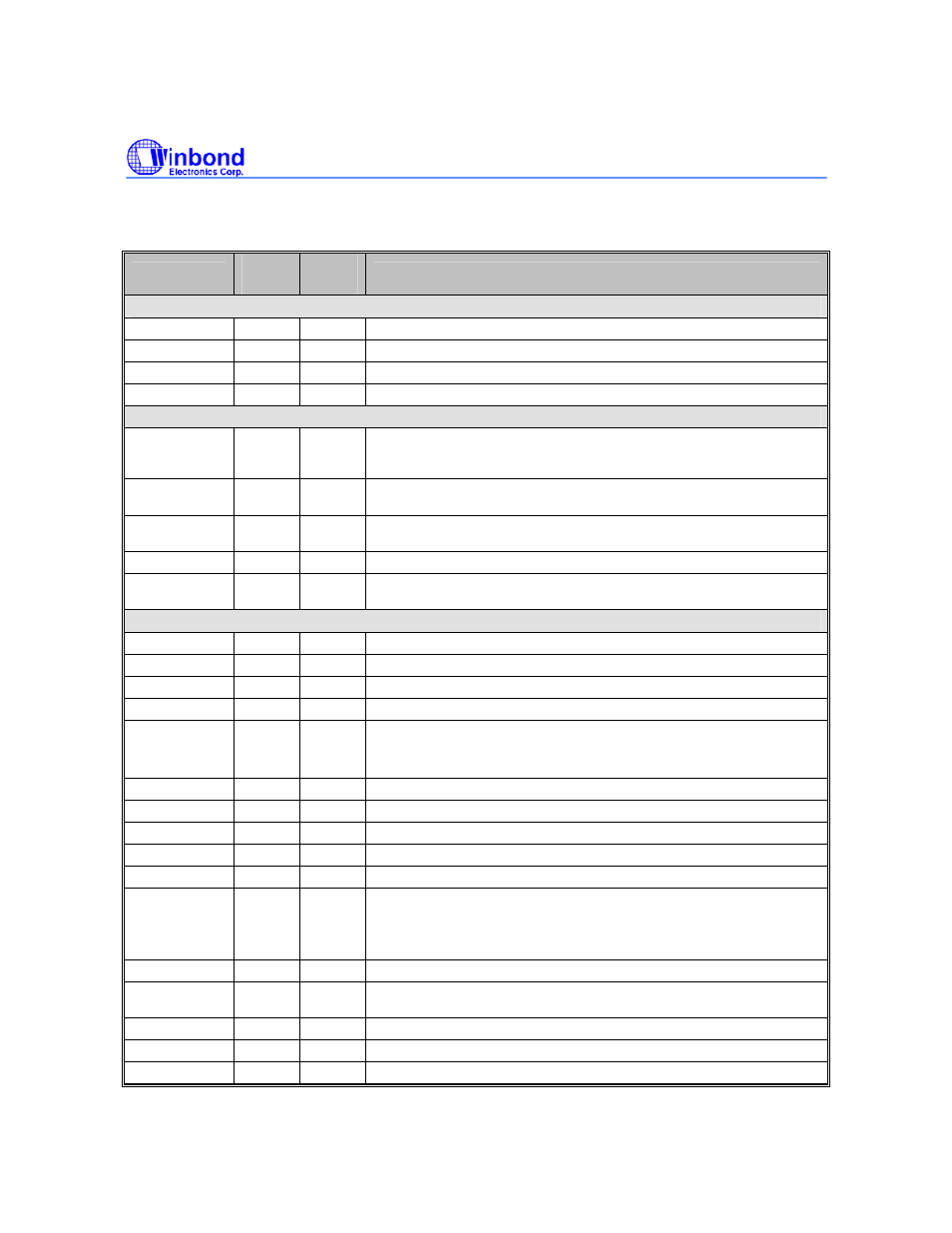

Table 6.1 W90N740 Pins Description

PIN NAME

IO

TYPE

PAD

TYPE

DESCRIPTION

System Clock & Reset

EXTAL

I

-

External Clock / Crystal Input

XTAL O

-

Crystal

Output

MCLK

O

-

System Master Clock Out, SDRAM clock

nRESET

I

-

System Reset, active-low

TAP Interface

TCK ID

internal

pull-

down

JTAG Test Clock,

TMS IU

internal

pull-up

JTAG Test Mode Select,

TDI IU

internal

pull-up

JTAG Test Data in,

TDO

O

-

JTAG Test Data out

nTRST IU

internal

pull-up

JTAG Reset, active-low,

External Bus Interface

A [24:22]

O

-

Address Bus (MSB) of external memory and IO devices

A [21:0]

IO

-

Address Bus of external memory and IO devices

D [31:16]

IO

-

Data Bus (MSB) of external memory and IO device,

D [15:0]

IO

-

Data Bus (LSB) of external memory and IO device

nWBE [3:0]/

SDQM [3:0]

IO -

Write Byte Enable for specific device(nECS[3:0]),

Data input/output Mask signal for SDRAM (nSCS[1:0]), active-low These pins

are always Output in normal mode, and Input type in internal SRAM test mode.

nSCS [1:0]

O

-

SDRAM chip select for two external banks, active-low.

nSRAS

O

-

Row Address Strobe for SDRAM, active-low

nSCAS

O

-

Column Address Strobe for SDRAM, active-low

nSWE

O

-

SDRAM Write Enable, active-low

MCKE

O

-

SDRAM Clock Enable, active-high

EMREQ ID

internal

pull-

down

External Master Bus Request

This is used to request external bus. When EMACK active, indicates the bus

grants the bus, chip drives all the output pins of the external bus to high

impedance.

EMACK

O

-

External Bus Acknowledge

nWAIT

IU

internal

pull-up

External Wait, active-low

nBTCS

O

-

ROM/Flash Chip Select, active-low

nECS [3:0]

IO

-

External I/O Chip Select, active-low.

nOE

O

-

ROM/Flash, External Memory Output Enable, active-low