Rainbow Electronics W90N740 User Manual

Page 31

W90N740

Publication Release Date: November 26, 2004

- 27 -

Revision A4

7.2.5 Bus

Arbitration

The W90N740’s internal function blocks or external devices can request mastership of the system bus

and then hold the system bus in order to perform data transfers. The design of W90N740 bus allows only

one bus master at a time, a bus controller is required to arbitrate when two or more internal units or

external devices simultaneously request bus mastership. When bus mastership is granted to an internal

function block or an external device, other pending requests are not acknowledged until the previous bus

master has released the bus.

W90N740 supports two priority modes, the Fixed Priority Mode and the Rotate Priority Mode,

depends on the PRTMOD bit setting.

7.2.5.1 Fixed Priority Mode

In Fixed Priority Mode (PRTMOD = 0, default value), to facilitate bus arbitration, priorities are assigned

to each internal W90N740 function block. The bus controller arbitration requests for the bus mastership

according to these fixed priorities. In the event of contention, mastership is granted to the function block

with the highest assigned priority. These priorities are listed in Table 7.2.15.

W90N740 allows raising ARM Core priority to second if an unmasked interrupt occurred. If IPEN bit, Bit

22 of the Arbitration Control Register (ARBCON), is set to “0”, the priority of ARM Core is fixed to

lowest. If IPEN bit is set to “1” and if no unmasked interrupt request, then the ARM Core’s priority is still

lowest and the IPACT = 0, Bit 23 of the Arbitration Control Register (ARBCON) ; If there is an

unmasked interrupt request, then the ARM Core’s priority is raised to second and IPACT = 1.

If IPEN is set, an interrupt handler will normally clear IPACT at the end of the interrupt routine to allow an

alternate bus master to regain the bus; however, if IPEN is cleared, no additional action need be taken in

the interrupt handler. The IPACT bit can be read and write. Writing with “0”, the IPACT bit is cleared, but

it will be no effect as writing with “1”.

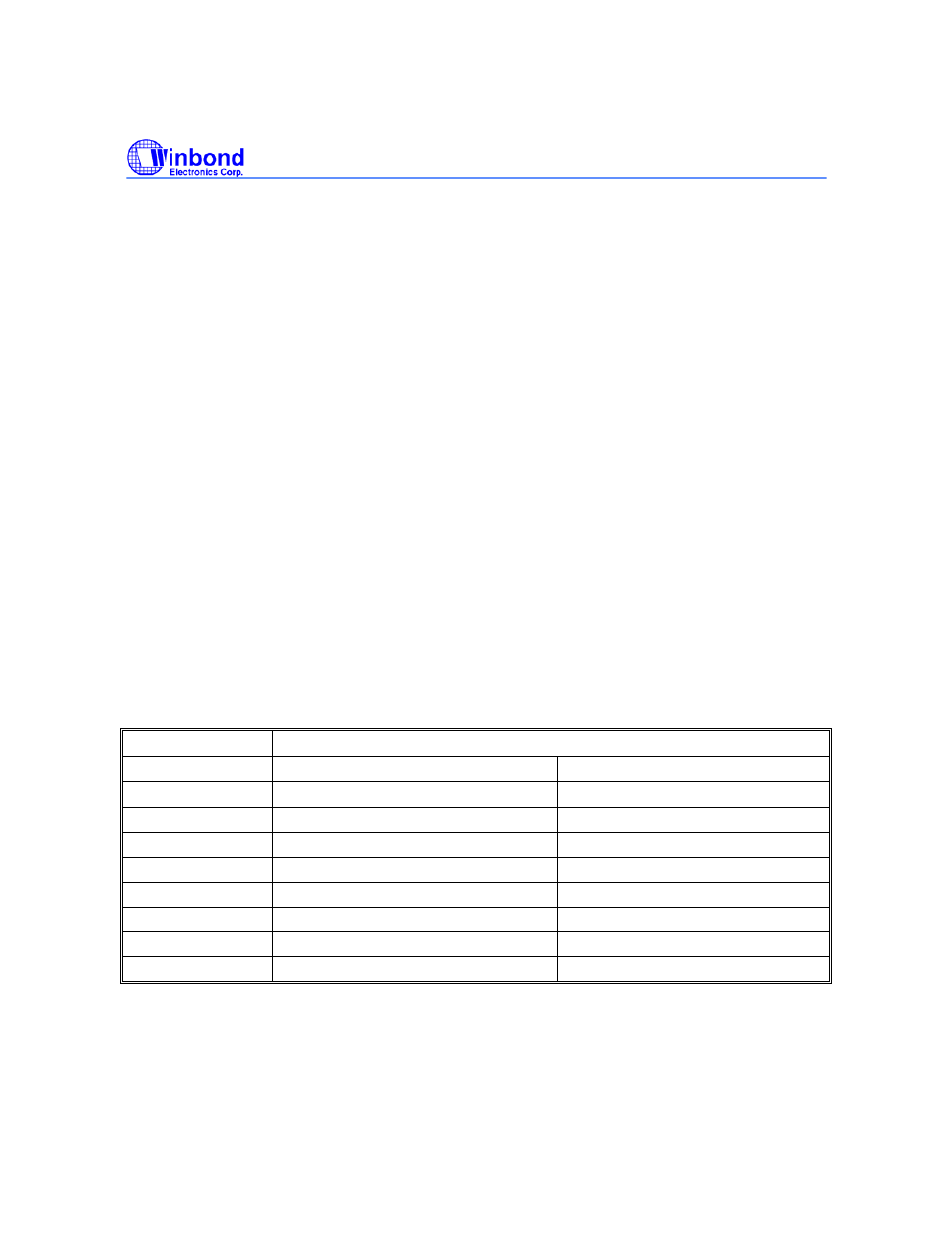

Table 7.2.15 Bus Priorities for Arbitration in Fixed Priority Mode

Bus

Function Block

Priority

IPACT = 0

IPEN = 1 and IPACT = 1

1 (Highest)

External Bus Master

External Bus Master

2

NAT Accelerator

ARM Core

3

General DMA0

NAT Accelerator

4

General DMA1

General DMA0

5

EMC0 DMA

General DMA1

6

EMC1 DMA

EMC0 DMA

7

USB (Host)

EMC1 DMA

8 (Lowest)

ARM Core

USB (Host)