Rainbow Electronics W90N740 User Manual

Page 15

W90N740

Publication Release Date: November 26, 2004

- 11 -

Revision A4

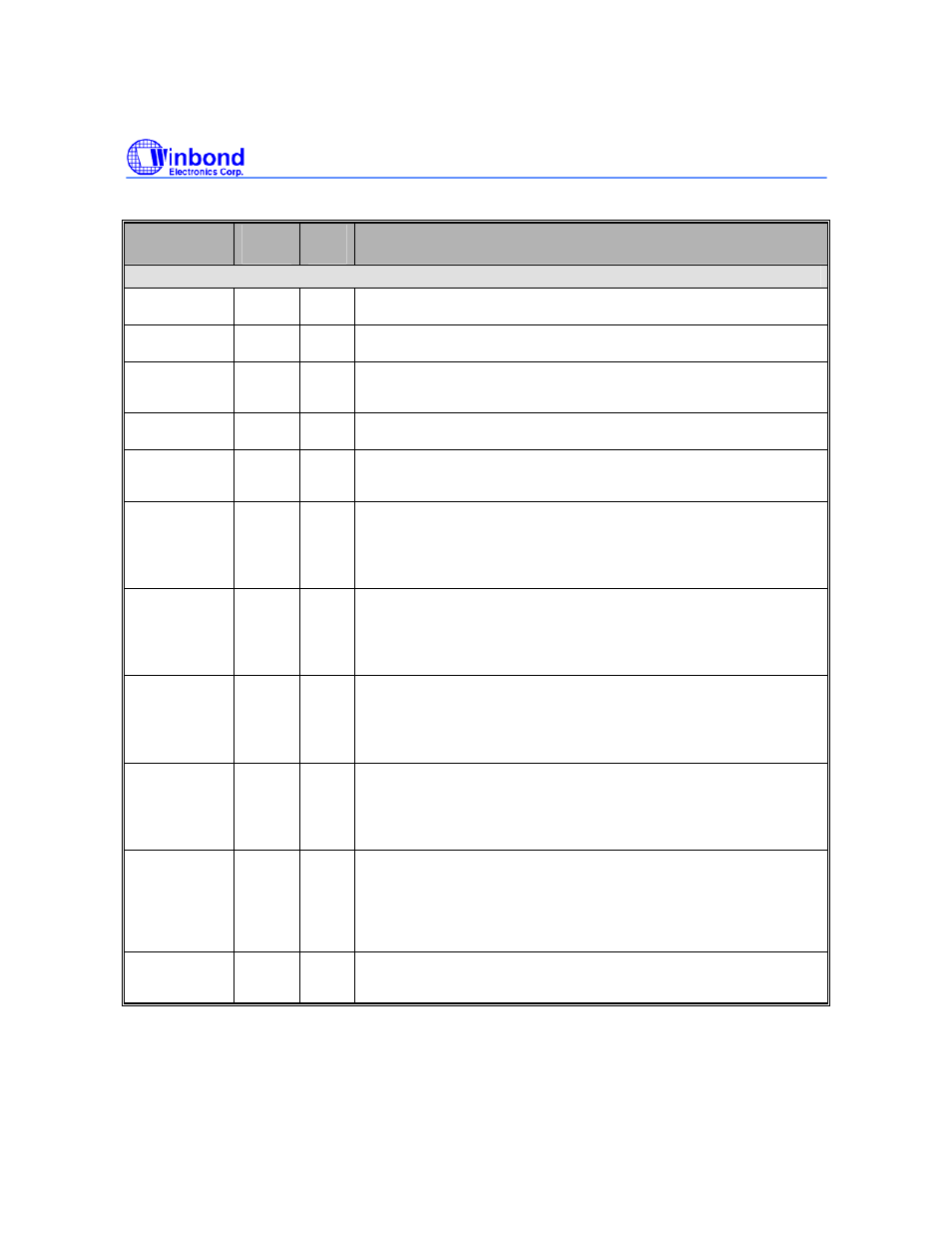

Pins Description, continued

PIN NAME

IO

TYPE

PAD

TYPE

DESCRIPTION

Ethernet Interface (0)

MDC0 O

-

MII Management Data Clock for Ethernet 0. It is the reference clock of MDIO0.

Each MDIO0 data will be latched at the rising edge of MDC0 clock.

MDIO0 IO

-

MII Management Data I/O for Ethernet 0. It is used to transfer MII control and

status information between PHY and MAC.

COL0

I

-

Collision Detect for Ethernet 0 in MII mode. This shall be asserted by PHY upon

detecting a collision happened over the medium. It will be asserted and lasted until

collision condition vanishes.

CRS0

I

-

Carrier Sense for Ethernet 0 in MII mode. In RMII mode, external pull-up is

necessary.

TX0_CLK I

-

Transmit Data Clock for Ethernet 0 in MII mode.

TX0_CLK is driven by PHY and

provides the timing reference for TX0_EN and TX0D. The clock will be 25MHz or

2.5 MHz.

TX0D [3:0]/

--, R0_TXD

[1:0]

O

-

Transmit Data bus (4-bit) for Ethernet 0 in MII mode. The nibble transmit data bus

is synchronized with TX0_CLK. It should be latched by PHY at the rising edge of

TX0_CLK.

In RMII mode, TX0D [1:0] are used as R0_TXD [1:0], 2-bit Transmit Data bus for

Ethernet 0;

TX0_EN /

R0_TXEN

O

-

Transmit Enable for Ethernet 0 in MII. It indicates the transmit activity to external

PHY. It will be synchronized with TX0_CLK.

In RMII mode, R0_TXEN shall be asserted synchronously with the first nibble of

the preamble and shall remain asserted while all di-bits to be transmitted are

presented. Of course, it is synchronized with R0_REFCLK.

RX0_CLK /

R0_REFCLK

I

-

Receive Data Clock for Ethernet 0 in MII mode When it is used as a received clock

pin, it is from PHY. The clock will be either 25 MHz or 2.5 MHz. The minimum duty

cycle at its high or low state should be 35% of the nominal period for all conditions.

In RMII mode, this pin is used as R0_REFCLK, Reference Clock;

The clock shall

be 50MHz +/- 50 ppm with minimum 35% duty cycle at high or low state.

RX0D [3:0] /

--, R0_RXD

[1:0]

I

-

Receive Data bus (4-bit) for Ethernet 0 in MII mode. They are driven by external

PHY, and should be synchronized with RX0_CLK and valid only when RX0_DV is

valid.

In RMII mode, RX0D [1:0] are used as R0_RXD [1:0], 2-bit Receive Data bus for

Ethernet 0;

RX0_DV /

R0_CRSDV

I

-

Receive Data Valid for Ethernet 0 in MII mode. It will be asserted when received data

is coming and present, and de-asserted at the end of the frame.

In RMII mode, this pin is used as the R0_CRSDV, Carrier Sense / Receive Data

Valid for Ethernet 0. The R0_CRSDV shall be asserted by PHY when the receive

medium is non-idle. Loss of carrier shall result in the de-assertion of R0_CRSDV

synchronous to the cycle of R0_REFCLK, and only on nibble boundaries.

RX0_ERR

I

-

Receive Data Error for Ethernet 0 in MII mode. It indicates a data error detected by

PHY. The assertion should be lasted for longer than a period of RX0_CLK. When

RX0_ERR is asserted, the MAC will report a CRC error.