Rainbow Electronics W90N740 User Manual

Page 151

W90N740

Publication Release Date: November 26, 2004

- 147 -

Revision A4

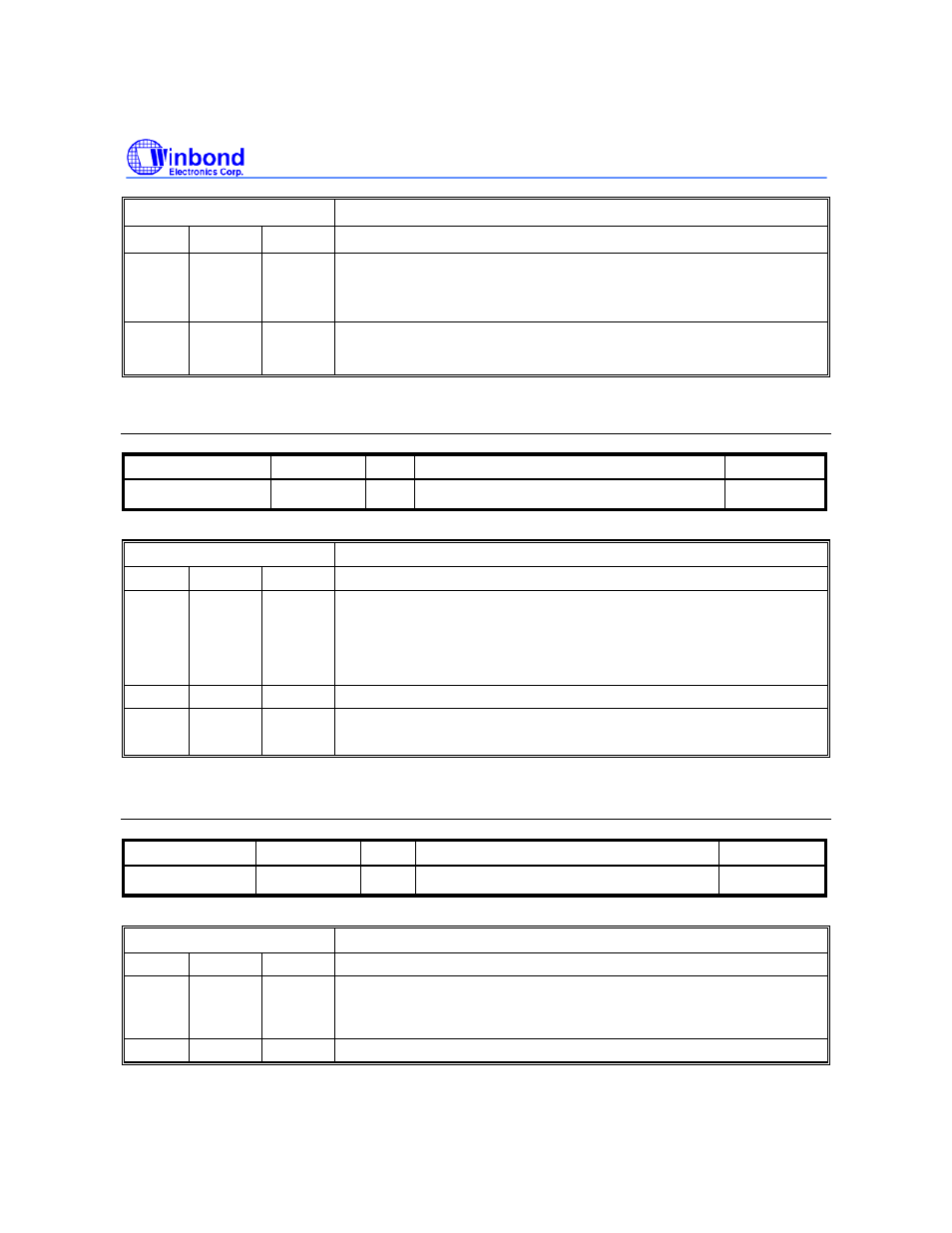

Register: HcFmInterval

Bits Reset R/W Description

30-16

FSLargestDataPacket

This field specifies a value that is loaded into the Largest Data Packet

Counter at the beginning of each frame.

31

FrameIntervalToggle

This bit is toggled by HCD when it loads a new value into FrameInterval.

Host Controller Frame Remaining Register (HcFrameRemaining)

Register Address

R/W

Description

Reset

Value

HcFrameRemaining 0xFFF0.5038

R Host Controller Frame Remaining Register 0x0000.0000

Register: HcFrameRemaining

Bits Reset R/W+

Description

13-0 0b R

FrameRemaining

When the Host Controller is in the U

SB

O

PERATIONAL

state, this 14-bit field

decrements each 12 MHz clock period. When the count reaches 0, (end of

frame) the counter reloads with FrameInterval. In addition, the counter

loads when the Host Controller transitions into U

SB

O

PERATIONAL

.

30-14

0h

-

Reserved. Read/Write 0's

31 0b R

FrameRemainingToggle

Loaded with FrameIntervalToggle when FrameRemaining is loaded.

Host Controller Frame Number Register (HcFmNumber)

Register Address

R/W

Description

Reset

Value

HcFmNumber 0xFFF0.503C

R

Host Controller Frame Number Register

0x0000.0000

Register: HcFmNumber

Bits Reset R/W Description

15-0 0b R

FrameNumber

This 16-bit incrementing counter field is incremented coincident with the

loading of FrameRemaining. The count rolls over from ‘FFFFh’ to ‘0h.’

31-16

0h

-

Reserved. Read/Write 0's