Rainbow Electronics W90N740 User Manual

Page 146

W90N740

- 142 -

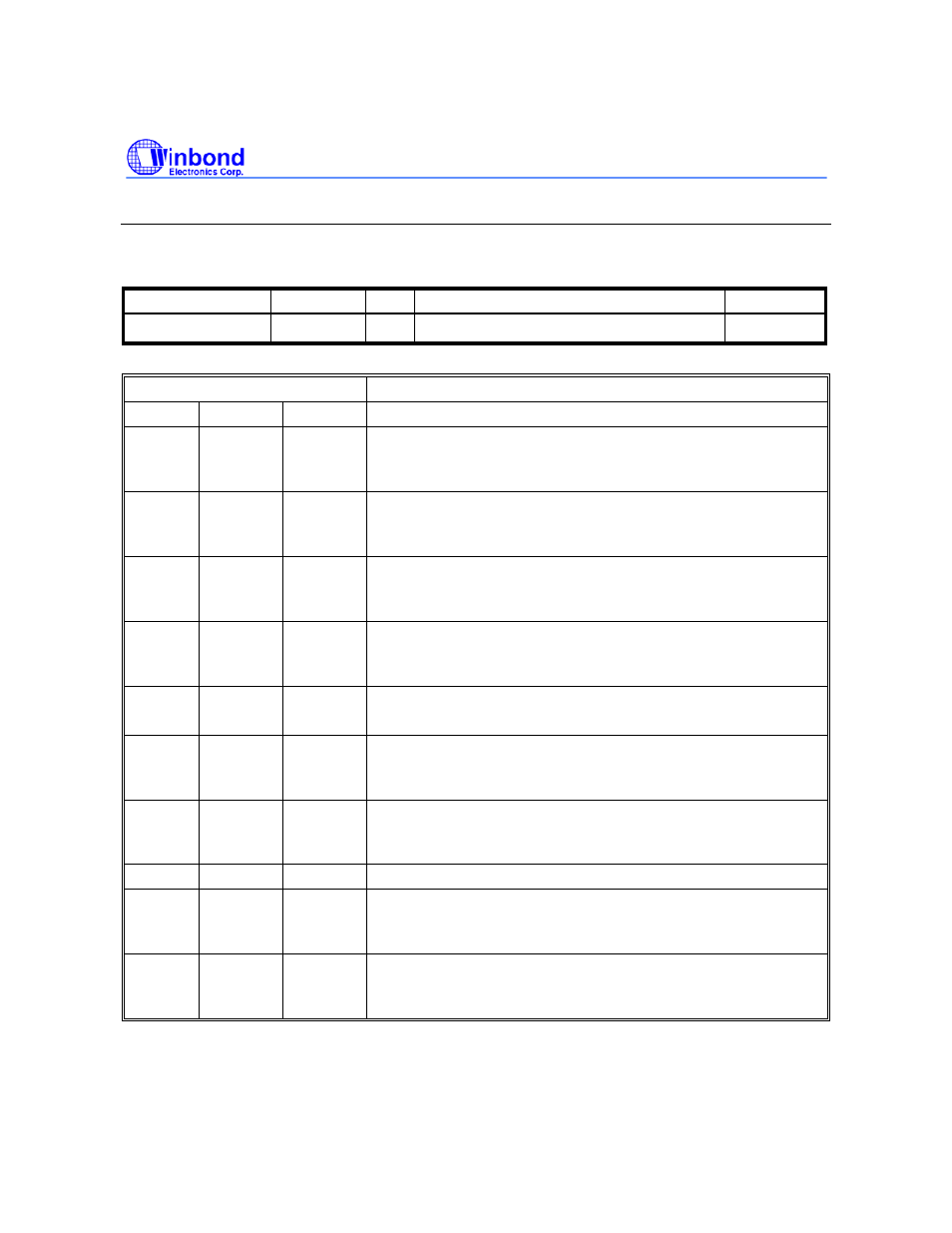

Host Controller Interrupt Enable Register (HcInterruptEnable)

Writing a ‘1’ to a bit in this register sets the corresponding bit, while writing a ‘0’ leaves the bit

unchanged.

Register Address

R/W

Description

Reset

Value

HcInterruptEnable 0xFFF0.5010

R/W Host Controller Interrupt Enable Register

0x0000.0000

Register: HcInterruptEnable

Bits Reset R/W

Description

0 0b R/W

SchedulingOverrunEnable

0: Ignore

1: Enable interrupt generation due to Scheduling Overrun.

1 0b R/W

WritebackDoneHeadEnable

0: Ignore

1: Enable interrupt generation due to Write-back Done Head.

2 0b R/W

StartOfFrameEnable

0: Ignore

1: Enable interrupt generation due to Start of Frame.

3 0b R/W

ResumeDetectedEnable

0: Ignore

1: Enable interrupt generation due to Resume Detected.

4 0b R/W

UnrecoverableErrorEnable

This event is not implemented. All writes to this bit are ignored.

5 0b R/W

FrameNumberOverflowEnable

0: Ignore

1: Enable interrupt generation due to Frame Number Overflow.

6 0b R/W

RootHubStatusChangeEnable

0: Ignore

1: Enable interrupt generation due to Root Hub Status Change.

29-7

0h

-

Reserved. Read/Write 0's

30 0b R/W

OwnershipChangeEnable

0: Ignore

1: Enable interrupt generation due to Ownership Change.

31 0b R/W

MasterInterruptEnable

This bit is a global interrupt enable. A write of ‘1’ allows interrupts to be

enabled via the specific enable bits listed above.