Rainbow Electronics W90N740 User Manual

Page 92

W90N740

- 88 -

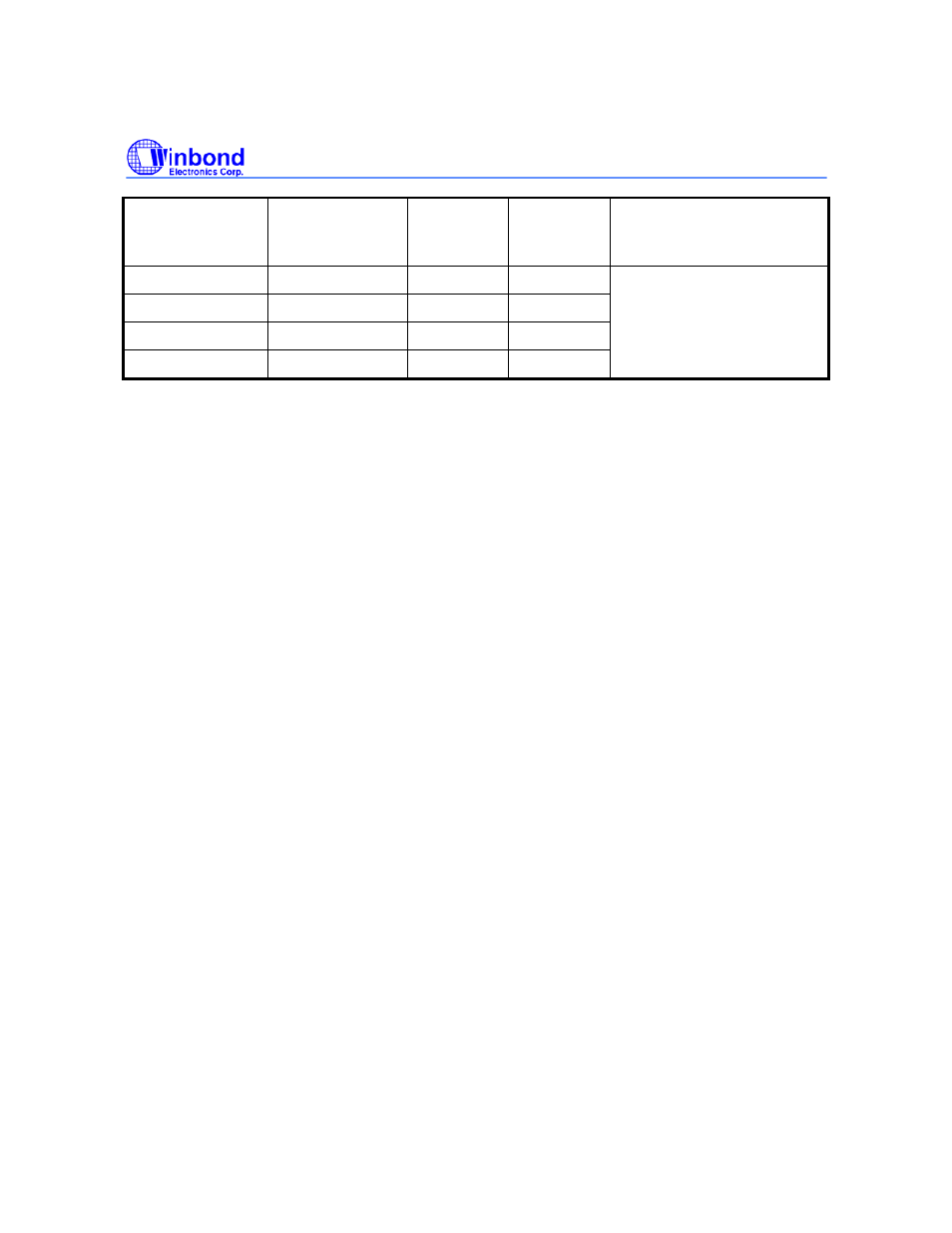

MAC 1 BIT [23:22]

LPCS: ENRMII

MAC 0 BIT

[23:22]

LPCS

*1

: ENRMII

MAC 1

INTERFACE

MAC 0

INTERFACE

NOTE

00 X0

MII

MII

00 X1

MII

RMII

01 X0

RMII

MII

01 X1

RMII

RMII

*1: the LPCS of MAC0 bit23

is undefined, which not

affect MAC 0 Interface.

LBK [21]: Loop Back

Default value: 0

Set this bit to enable MAC internal loop back mode.

OPMOD [20]: Operation Mode

Default value: 0

Set this bit to enable MAC to be operated at 100Mb/s. Clear this bit to enable MAC to be operated at

10Mb/s.

EnMDC [19]: Enable MDC signal

Default value: 0

Set this bit to enable MDC clock generation. Clear this bit to disable MDC clock generation.

If users want to access the MII management data, the EnMDC bit should be set to enable MDC clock.

FDUP [18]: Full Duplex

Default value: 0

Set this bit to perform the full duplex function.

Reserved [17]:

Default value: 0

SDPZ [16]: Send Pause

Default value: 0

Set this bit to send a pause command or other MAC control packet. The SDPZ bit will be automatically

cleared after the MAC control packet has been transmitted. Write zero to this bit has no effect.

NDEF [9]: No defer

Default value: 0

Set this bit to disable defer counter.

TXON [8]: Transmit On

Default value: 0

When this bit is set, the transmission process will be started. If the bit is clear, transmissions will stop

after the current packet is transmitted completely. Users should change the bit when the MAC is in idle

state.