Rainbow Electronics W90N740 User Manual

Page 63

W90N740

Publication Release Date: November 26, 2004

- 59 -

Revision A4

7.4 Cache

Controller

The W90N740 has an 8KB Instruction cache, 2KB Data cache, and 8 words write buffer. The I-Cache

and D-Cache are similar except the cache size. To enhance the hit ratio, these two caches are

configured two-way set associative addressing. Each cache has four words cache line size. When a miss

occurs, four words must be fetched consecutively from external memory. The replacement algorithm is a

LRU (Least Recently Used).

The W90N740 also provides a write buffer to improve system performance. The write buffer can buffer

up to eight words of data.

7.4.1 On-Chip

RAM

If I-Cache or D-Cache is disabled, it can be served as On-Chip RAM. If D-Cache is disabled, there has

2KB On-Chip RAM, its start address is 0xFFE02000. If I-Cache is disabled, there has 8KB On-Chip RAM

and the start address of this RAM is 0xFFE00000. If both the I-Cache and D-Cache are disabled, it has

10KB On-Chip RAM starting from 0xFFE00000.

The size of On-Chip RAM is depended on the I-Cache and D-Cache enable bits ICAEN, DCAEN in

Cache Control Register (CAHCON).

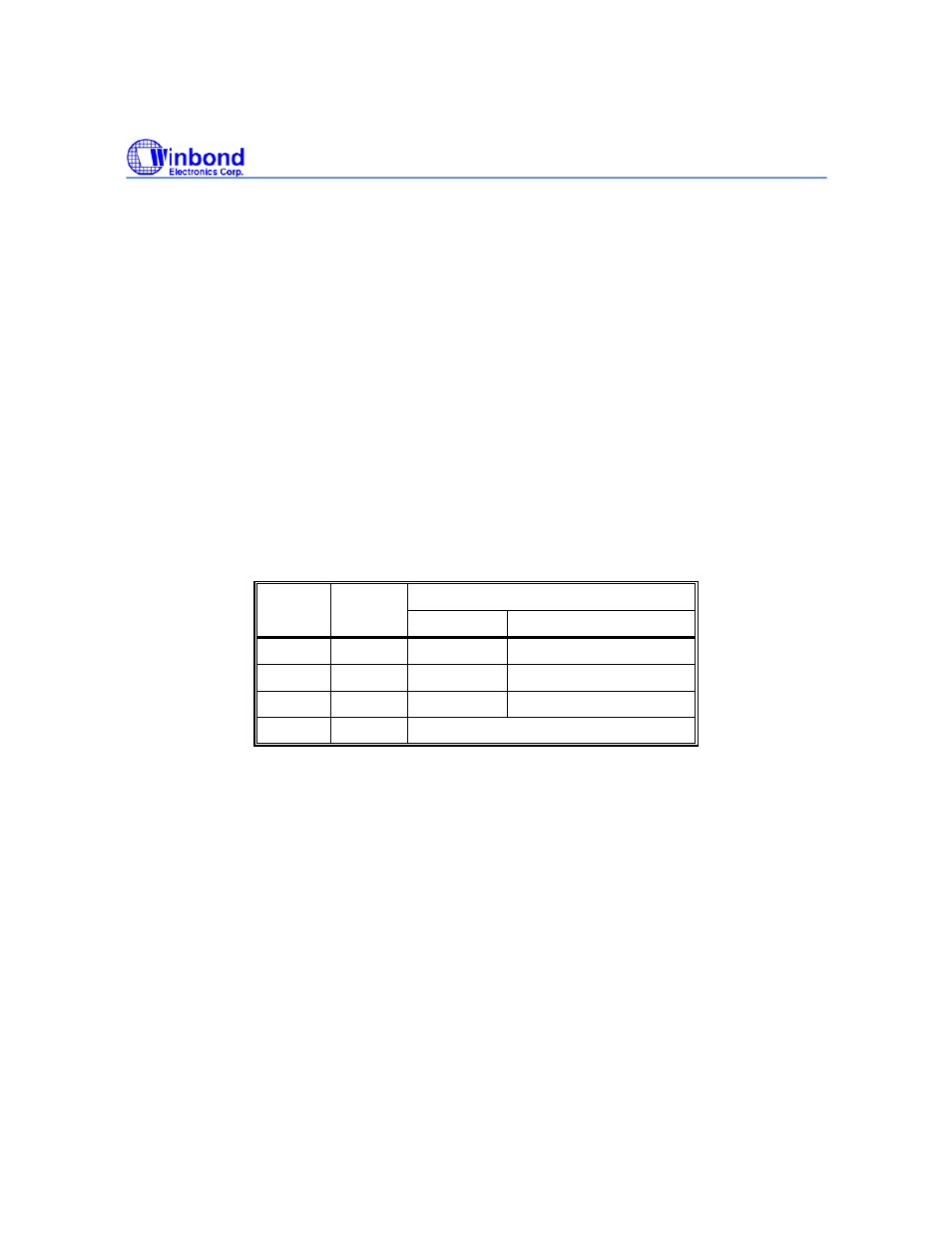

Table7.4.1 The size and start address of On-Chip RAM

ICAEN DCAEN

On-Chip

RAM

Size Start

Address

0 0 10KB 0xFFE0.0000

0 1 8KB 0xFFE0.0000

1 0 2KB 0xFFE0.2000

1 1

Unavailable

7.4.2 Non-Cacheable

Area

Although the cache affects the entire 2GB system memory, it is sometimes necessary to define non-

cacheable areas when the consistency of data stored in memory and the cache must be ensured. To

support this, the W90N740 provides a non-cacheable area control bit in the address field, A [31].

If A [31] in the ROM/FLASH, SDRAM, or external I/O bank’s access address is “0”, then the accessed

data is cacheable. If the A [31] value is “1”, the accessed data is non-cacheable.

7.4.3 Instruction

Cache

The Instruction cache (I-cache) is an 8K bytes two-way set associative cache. The cache organization is

256 sets, two lines per set, and four words per line. Cache lines are aligned on 4-word boundaries in

memory.