Rainbow Electronics W90N740 User Manual

Page 76

W90N740

- 72 -

Hit: current packet is hit with NAT entry table

The value is 1 if current packet IP/port is in the entry list. If NAT is disabled, the bit is reserved.

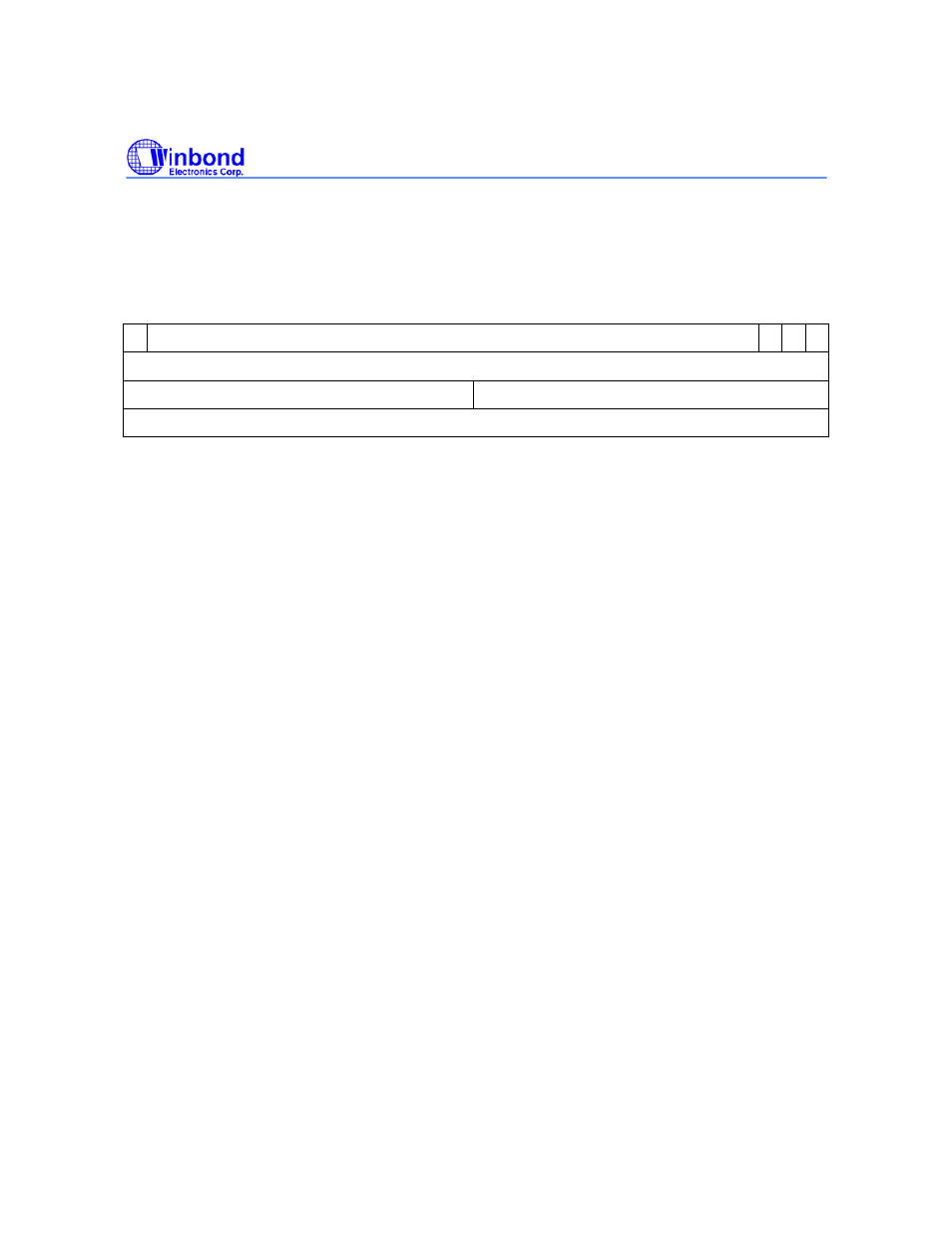

Tx Buffer Descriptor (TXBD)

3

1

3

0

1

6

1

5

3

2

1

0

O I

C P

Data Buffer Starting Address

Tx Status

Frame Length

Next Descriptor Starting Address

O: Ownership bit

0 = CPU 1 = DMA

W90N740 transmit DMA is allowed to access current descriptor if this bit is set to ‘1’ by the user driver

program. If the entire frame is transmitted successfully, then the ownership bit is cleared and the

ownership is granted to CPU.

I: MAC transmit interrupt enable after transmission complete of the frame

0 = Disable

1 = Enable

7.5.1.6 C: CRC mode bit

0 = Disable CRC mode

1 = Enable CRC mode

7.5.1.7 P: Padding mode bit

0 = Disable padding mode

1 = Enable padding mode

Data Buffer Starting Address

This field is the starting address of the frame data to be transmitted.

7.5.1.8 Tx Status: Transmit Status

This field is updated by the EMC after transmission.

7.5.1.9 Frame Length

This field is the size of the transmit frame.

Next Descriptor Starting Address

This field is the starting address of the next frame descriptor.