3 instruction address addressing, 1 relative addressing – NEC PD78F9488 User Manual

Page 66

CHAPTER 3 CPU ARCHITECTURE

66

User’s Manual U15331EJ4V1UD

3.3 Instruction Address Addressing

An instruction address is determined by the program counter (PC) contents. The PC contents are normally

incremented (+1 for each byte) automatically according to the number of bytes of an instruction to be fetched each

time another instruction is executed. When a branch instruction is executed, the branch destination information is set

to the PC and branched by the following addressing (for details of each instruction, refer to 78K/0S Series

Instructions User’s Manual (U11047E)).

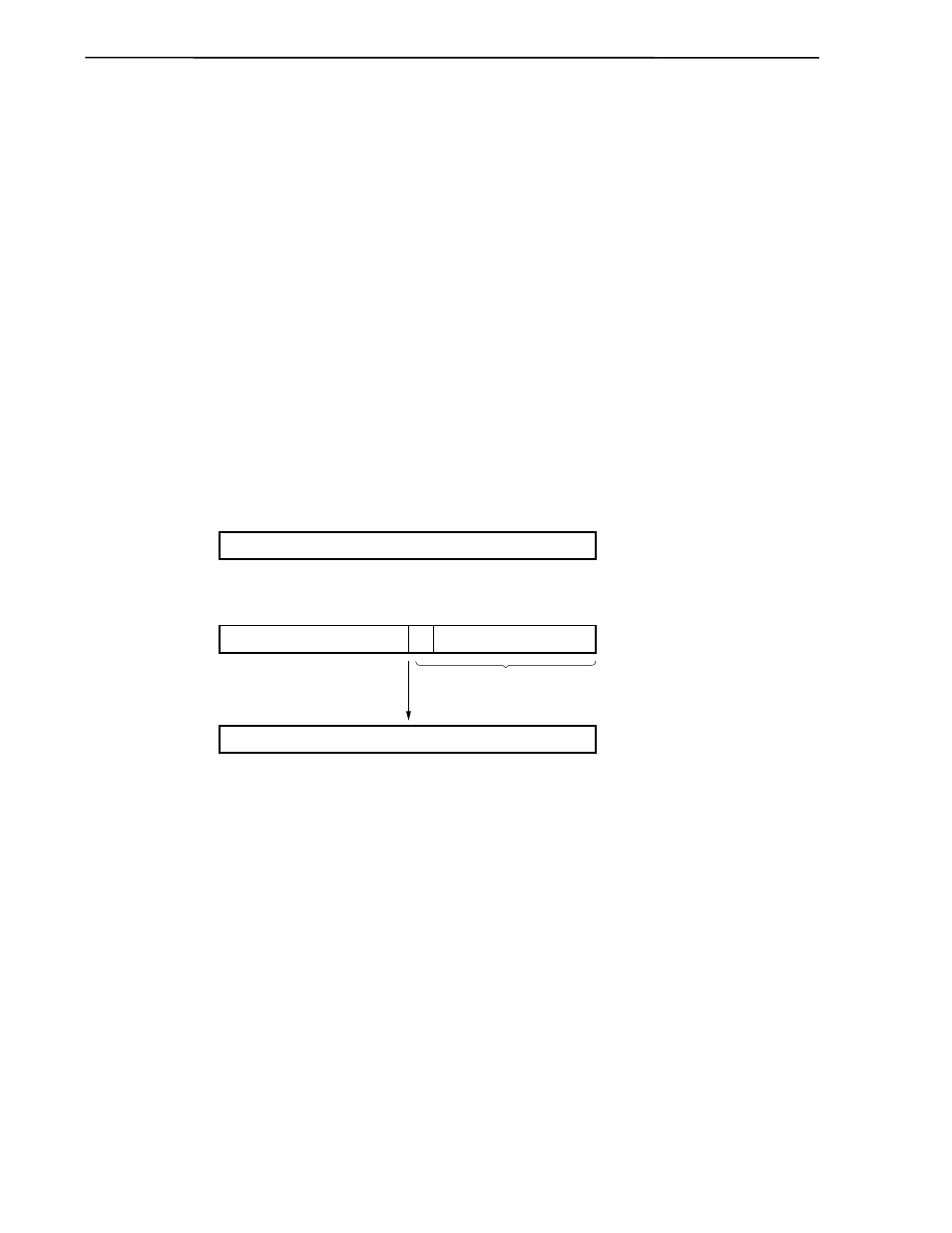

3.3.1 Relative addressing

[Function]

The value obtained by adding 8-bit immediate data (displacement value: jdisp8) of an instruction code to the

start address of the following instruction is transferred to the program counter (PC) and branched. The

displacement value is treated as signed two’s complement data (–128 to +127) and bit 7 becomes a sign bit.

This means that information is relatively branched to a location between –128 and +127, from the start address

of the next instruction when relative addressing is used.

This function is carried out when the BR $addr16 instruction or a conditional branch instruction is executed.

[Illustration]

15

0

PC

15

0

S

15

0

PC

+

8

7

6

α

jdisp8

When S = 0,

α

indicates all bits 0.

... PC is the start address of

the next instruction of

a BR instruction.

When S = 1,

α

indicates all bits 1.