NEC PD78F9488 User Manual

Page 132

CHAPTER 7 8-BIT TIMERS 50, 60, AND 61

User’s Manual U15331EJ4V1UD

132

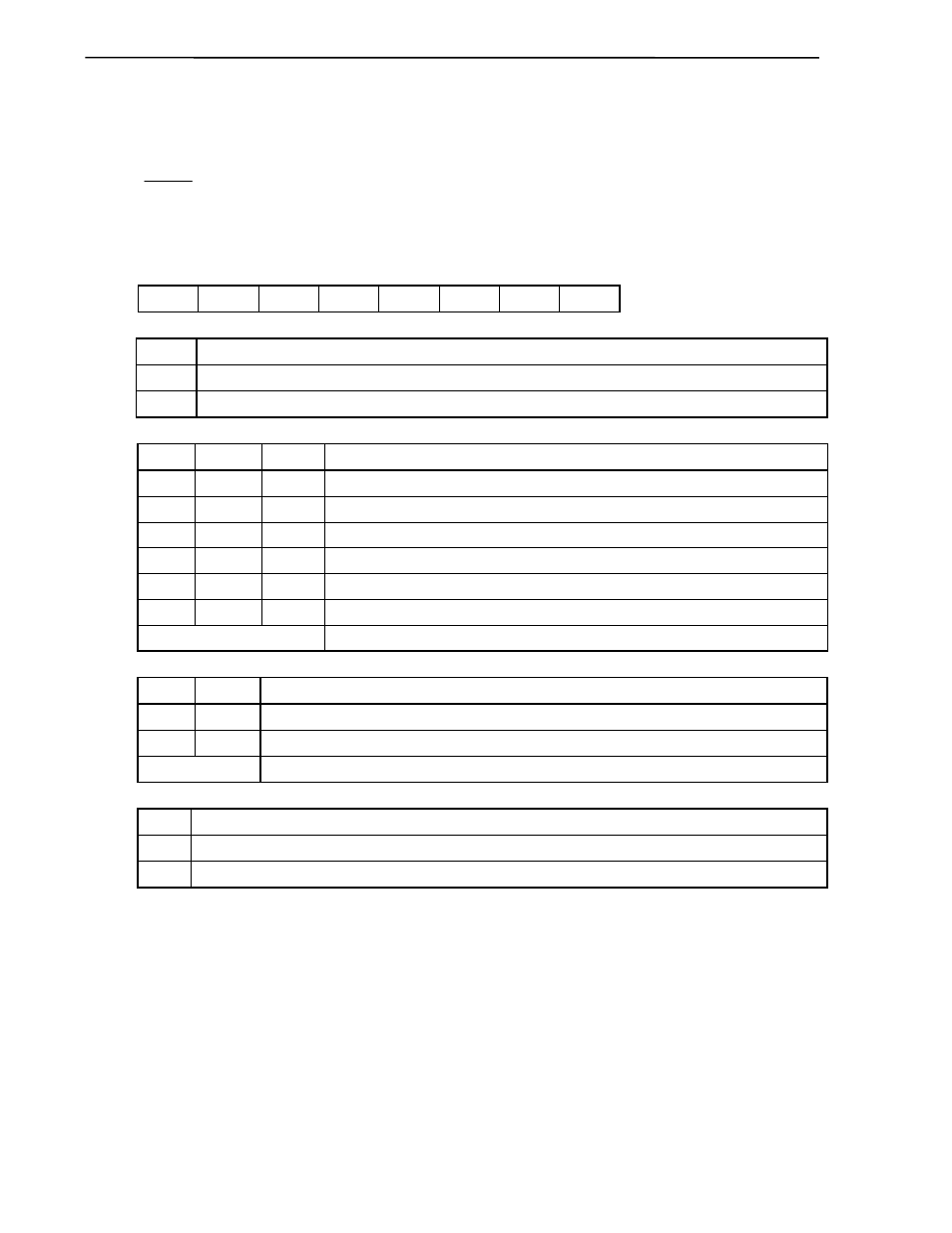

(4) 8-bit timer mode control register 61 (TMC61)

8-bit timer mode control register 61 (TMC61) is used to control the timer 61 count clock setting and the

operation mode setting.

TMC61 is set with a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to 00H.

Figure 7-9. Format of 8-Bit Timer Mode Control Register 61

Symbol

<7>

6 5 4 3 2 1

<0>

Address

After

reset

R/W

TMC61 TCE61

0

TCL612 TCL611 TCL610 TMD611 TMD610 TOE610

FF41H

00H

R/W

TCE61

Control of TM61 count operation

0

Clear TM61 count value and stop operation

1

Start count operation

TCL612

TCL611

TCL610

Selection of timer 61 count clock

Note

0 0 0

f

X

(5.0 MHz)

0 0 1

f

X

/2

4

(313 kHz)

0 1 0

f

TMI

0 1 1

f

TMI

/2

1 0 0

f

TMI

/2

2

1 0 1

f

TMI

/2

3

Other than above

Setting prohibited

TMD611

TMD610

Selection of operation mode for timer 61

Note

0

0

Stand-alone mode (8-bit counter mode)

1

0

PPG output mode

Other than above

Setting prohibited

TOE610

Control of timer output

0

Output

disabled

1

Output

enabled

Note To set the register in 24-bit event counter mode, the external input clock and stand-alone mode need to

be selected.

Caution To manipulate TMC61, follow the setting procedure below.

<1> Set the TM61 count operation to stop.

<2> Set the operation mode and count clock.

<3> The count operation starts.

Remarks 1. f

X

: Main system clock oscillation frequency

2. f

TMI

: External input clock frequency

3. The parenthesized values apply to operation at f

X

= 5.0 MHz.