2 operation as timer output – NEC PD78F9488 User Manual

Page 115

CHAPTER 6 16-BIT TIMER 20

User’s Manual U15331EJ4V1UD

115

6.4.2 Operation as timer output

16-bit timer 20 can invert the timer output repeatedly each time the free-running counter value reaches the value

set to CR20. Since this counter is not cleared and holds the count even after the timer output is inverted, the interval

time is equal to one cycle of the count clock set in TCL201 and TCL200.

To operate 16-bit timer 20 as a timer output, the following settings are required.

• Set P33 to output mode (PM33 = 0).

• Reset the output latch of P33 to 0.

• Set the count value in CR20.

• Set 16-bit timer mode control register 20 (TMC20) as shown in Figure 6-6.

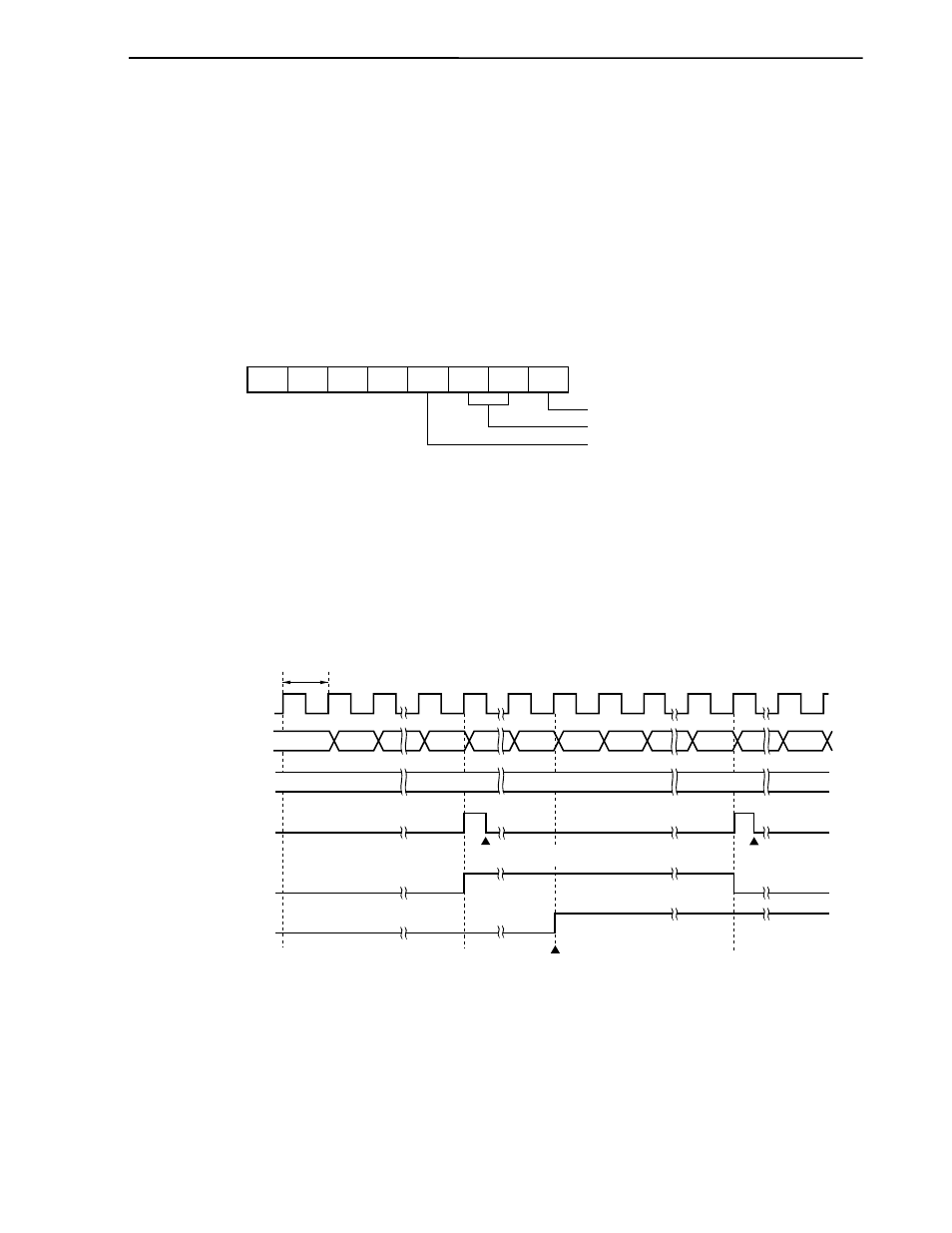

Figure 6-6. Settings of 16-Bit Timer Mode Control Register 20 for Timer Output Operation

−

0/1

0/1

0/1

1

0/1

0/1

1

TOD20 TOF20 CPT201 CPT200 TOC20 TCL201 TCL200 TOE20

TMC20

Setting of count clock (see Table 6-2)

Inverse enable of timer output data

TO20 output enable

Caution If both the CPT201 flag and CPT200 flag are set to 0, the capture edge operation is prohibited.

When the count value of 16-bit timer counter 20 (TM20) matches the value set in CR20, the output status of the

TO20 pin is inverted. This enables timer output. At that time, TM20 continues counting and an interrupt request

signal (INTTM20) is generated.

Figure 6-7 shows the timing of timer output (see Table 6-2 for the interval time of 16-bit timer 20).

Figure 6-7. Timer Output Timing

CR20

INTTM20

TOF20

N

N

N

N

N

t

0000H

N

FFFFH

N

0000H 0001H

0001H

TO20

Note

Count clock

TM20 count value

Interrupt

acknowledgement

Interrupt

acknowledgement

Overflow flag set

Note The initial value of TO20 becomes low level when output is enabled (TOE20 = 1).

Remark N = 0000H to FFFFH