NEC PD78F9488 User Manual

Page 318

CHAPTER 18 RESET FUNCTION

318

User’s Manual U15331EJ4V1UD

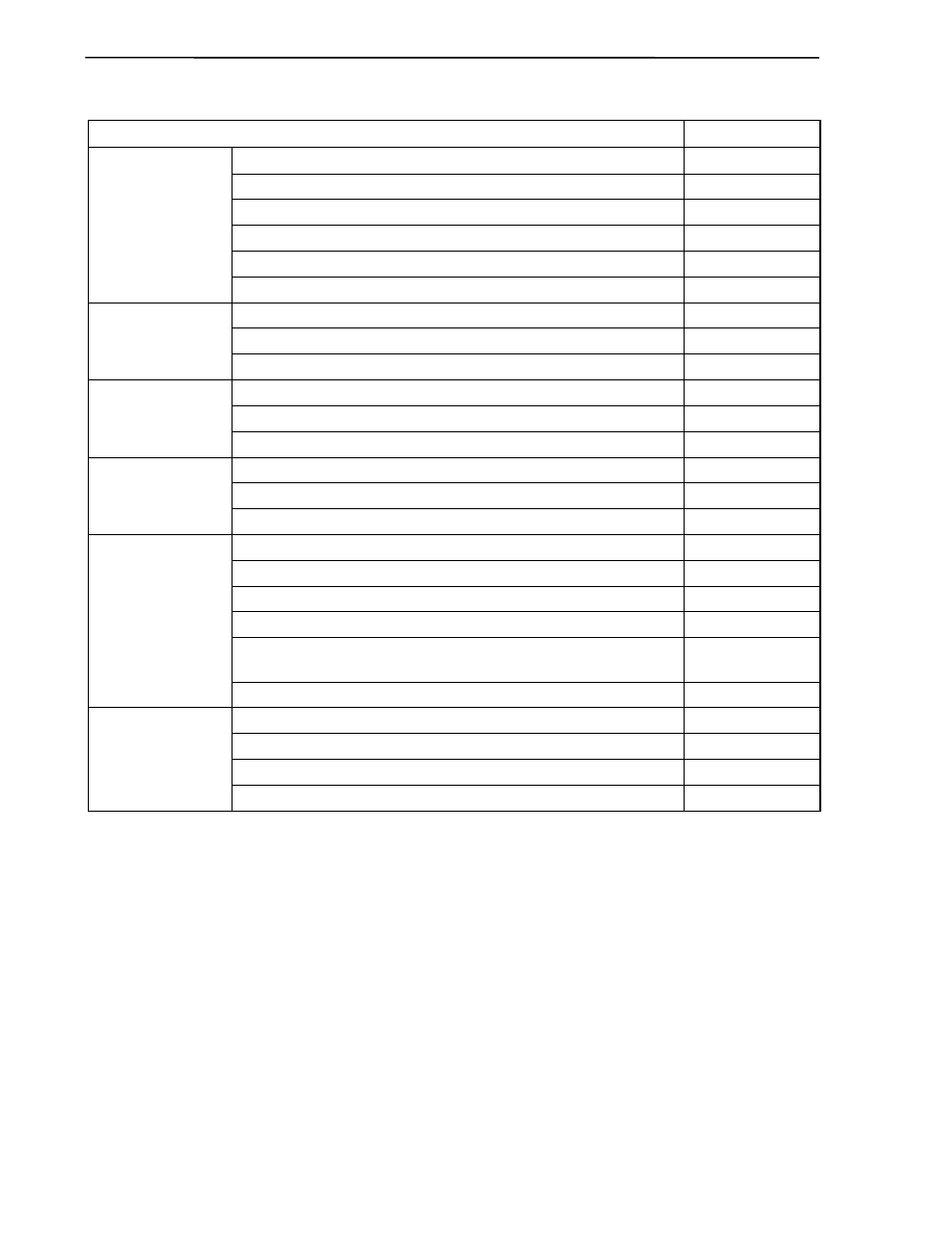

Table 18-1. Status of Hardware After Reset (2/2)

Hardware

Status After Reset

Operation mode register (CSIM1A0)

00H

Shift register (SIO1A0)

00H

Buffer memory (SBMEM0 to SBMEMF)

Undefined

Automatic data transmit/receive control register (ADTC0)

00H

Automatic data transmit/receive address pointer (ADTP0)

Undefined

Serial interface 1A0

Automatic data transmit/receive transfer interval specification register (ADTI0)

00H

Mode register (ADML0)

00H

Input channel specification register (ADS0)

00H

A/D converter

Conversion result register (ADCRL0)

0000H

Display mode register (LCDM0)

00H

Clock control register (LCDC0)

00H

LCD controller/driver

Voltage boost control register (LCDVA0)

00H

16-bit result storage register (MUL0)

Undefined

Data register (MRA0, MRB0)

Undefined

Multiplier

Control register (MULC0)

00H

Control register (RMCN)

00H

Data register (RMDR)

00H

Shift register reception counter register (RMSCR)

00H

Shift register (RMSR)

00H

Compare registers (RMGPHS, RMGPHL, RMDLS, RMDLL, RMDH0S,

RMDH0L, RMDH1S, RMDH1L)

00H

Remote controller

receiver

Note

End width selection register (RMER)

00H

Request flag register (IF0 to IF2)

00H

Mask flag register (MK0 to MK2)

FFH

External interrupt mode register (INTM0, INTM1)

00H

Interrupts

Key return mode registers (KRM00, KRM01

Note

) 00H

Note

µPD789489 and 78F9489 only