NEC PD78F9488 User Manual

Page 129

CHAPTER 7 8-BIT TIMERS 50, 60, AND 61

User’s Manual U15331EJ4V1UD

129

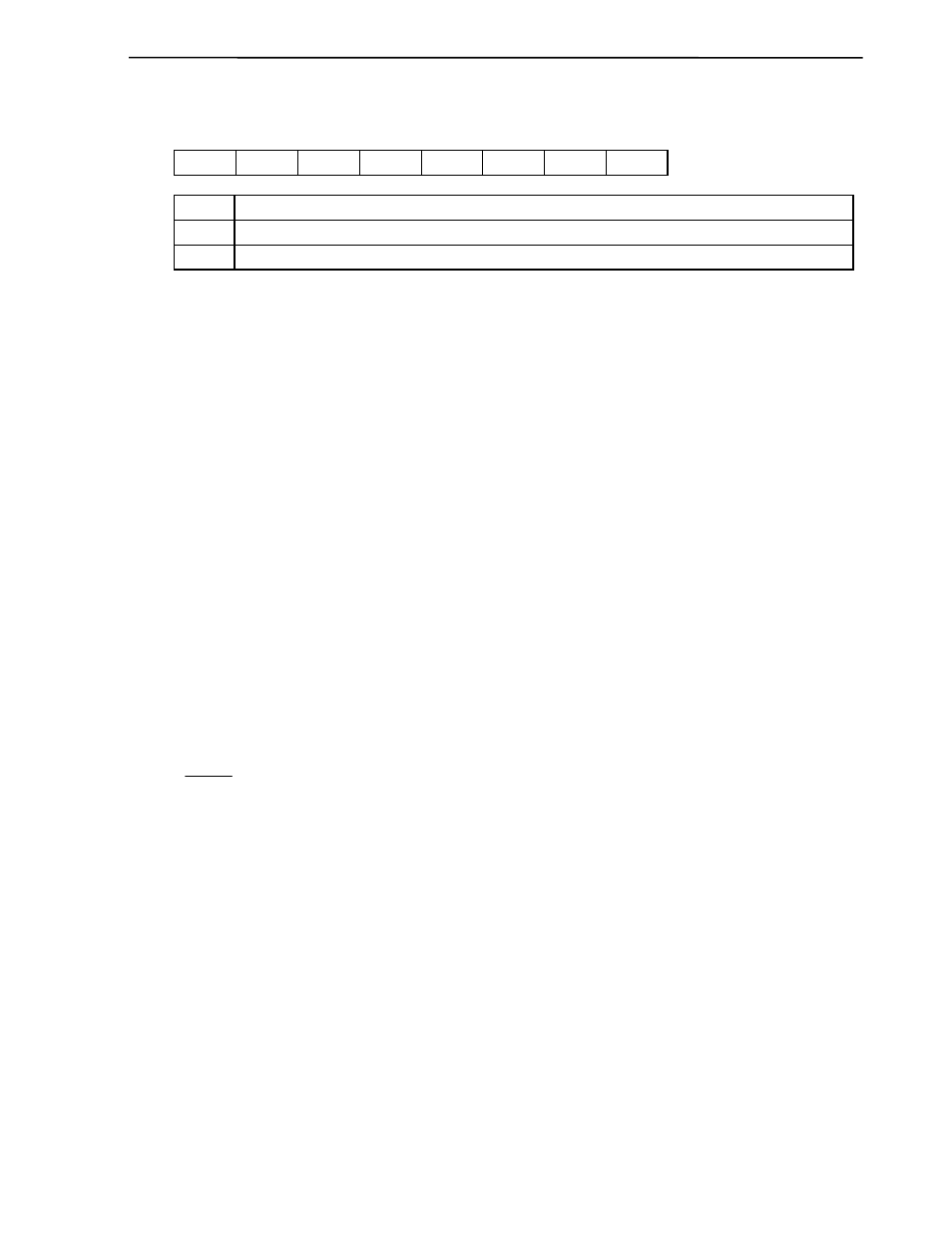

Figure 7-6. Format of 8-Bit Timer Mode Control Register 50 (2/2)

Symbol

<7>

<6>

5 4 3 2 1

<0>

Address

After

reset

R/W

TMC50 TCE50 TEG50 TCL502 TCL501 TCL500 TMD501

TMD500

TOE50 FF4DH

00H

R/W

TOE50

Control of timer output

Note 4

0

Output disabled

1

Output

enabled

Notes 1. Since the count operation is controlled by TCE60 (bit 7 of TMC60) in cascade connection mode,

any setting for TCE50 is ignored.

2. Selection of both edges is valid only in PWM mode. In 8-bit counter mode or cascade connection

mode, even if TEG50 is set to 1, counting occurs at the rising edge.

3. The operation mode selection is set by a combination of the TMC50 and TMC60 registers.

4. Since timer 50 output is disabled in cascade connection mode, set TOE50 to 0.

Cautions 1. In cascade connection mode, the timer 60 output signal is forcibly selected for the count

clock.

2. To manipulate TMC50, follow the setting procedure below.

<1> Set the TM50 count operation to stop.

<2> Set the operation mode and count clock.

<3> The count operation starts.

Remarks 1. f

X

: Main system clock oscillation frequency

2. f

XT

: Subsystem clock oscillation frequency

3. The parenthesized values apply to operation at f

X

= 5.0 MHz or f

XT

= 32.768 kHz.

4.

×: don’t

care

(2) 8-bit timer mode control register 60 (TMC60)

8-bit timer mode control register 60 (TMC60) is used to control the timer 60 count clock setting and the

operation mode setting.

TMC60 is set with a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to 00H.