NEC PD78F9488 User Manual

Page 121

CHAPTER 7 8-BIT TIMERS 50, 60, AND 61

User’s Manual U15331EJ4V1UD

121

(5) PPG output mode (PPG: Programmable Pulse Generator)

Pulses are output using any cycle or duty ratio (pulse width) set (both the cycle and pulse width are

programmable).

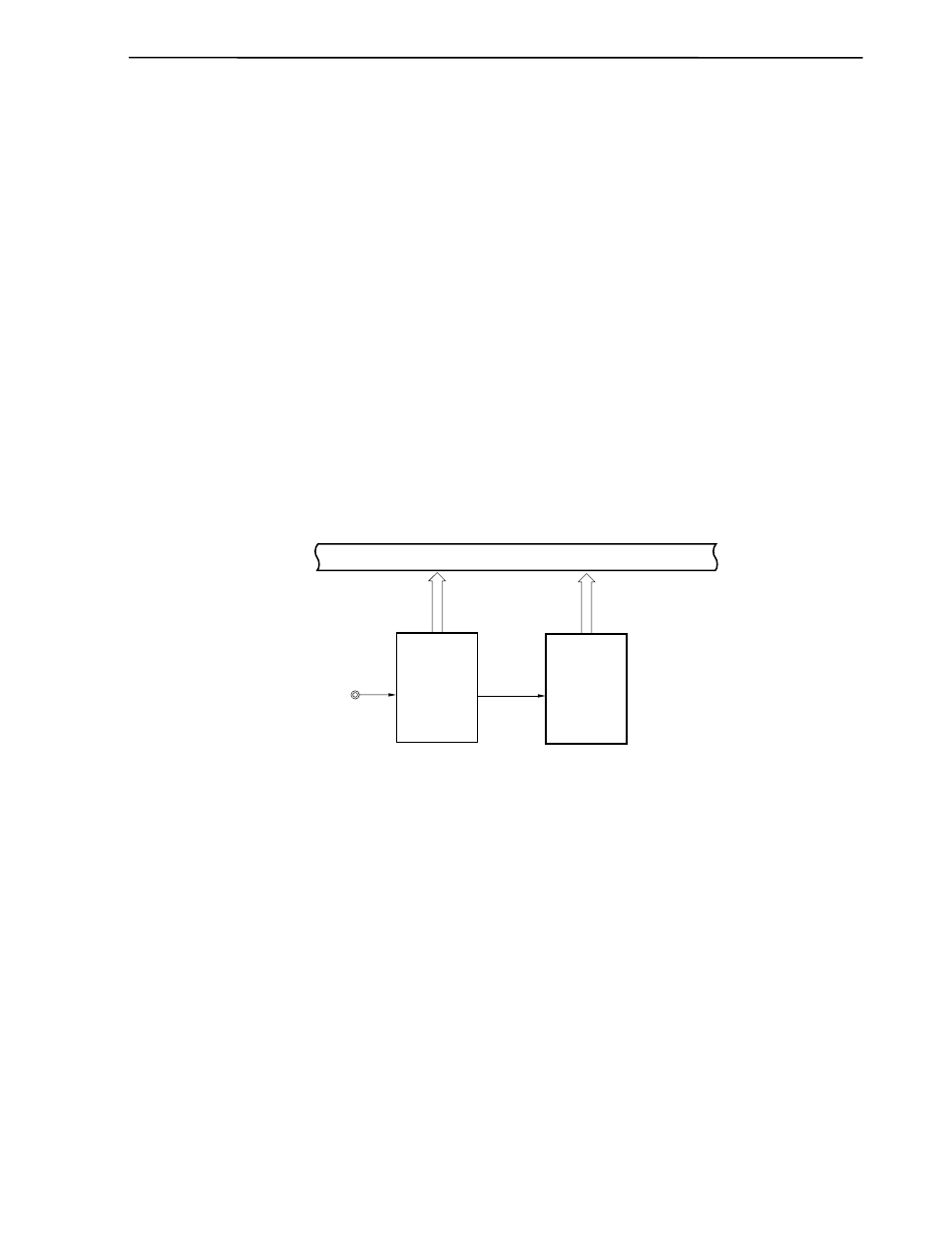

(6) 24-bit event counter mode

Operation as an external event counter with 24-bit resolution is enabled using 16-bit timer 20 and timer 61.

However, this mode operates only as a counter read function.

There is no compare, match, or clear function.

<1> Select the timer 61 interrupt signal for the count clock of 16-bit timer 20 (TCL201 = 0, TCL200 = 0)

<2> Set timer 61 in stand-alone mode (TMD611 = 0)

Select the external clock input from pin TMI61 for the count clock of timer 61

((TCL612 = 0, TCL611 = 1) or (TCL612 = 1, TCL611 = 0))

<3> Set CR61 to FFH

<4> Read the current count value of 16-bit timer 20

(16-bit timer 20 does not have a count clear function and is counting constantly)

<5> Enable timer 61 count operation (TCE61 = 1)

Figure 7-1. Block Diagram of 24-Bit Event Counter

Internal bus

TMI61/TO61

/INTP2/P32

Timer read

Timer read

Timer 61

(lower 8 bits)

Timer 20

(higher 16 bits)

Select external clock

for count clock

Select timer 61 interrupt

signal for count clock