NEC PD78F9488 User Manual

Page 272

CHAPTER 15 REMOTE CONTROLLER RECEIVER (

µ

PD789489, 78F9489 ONLY)

User’s Manual U15331EJ4V1UD

272

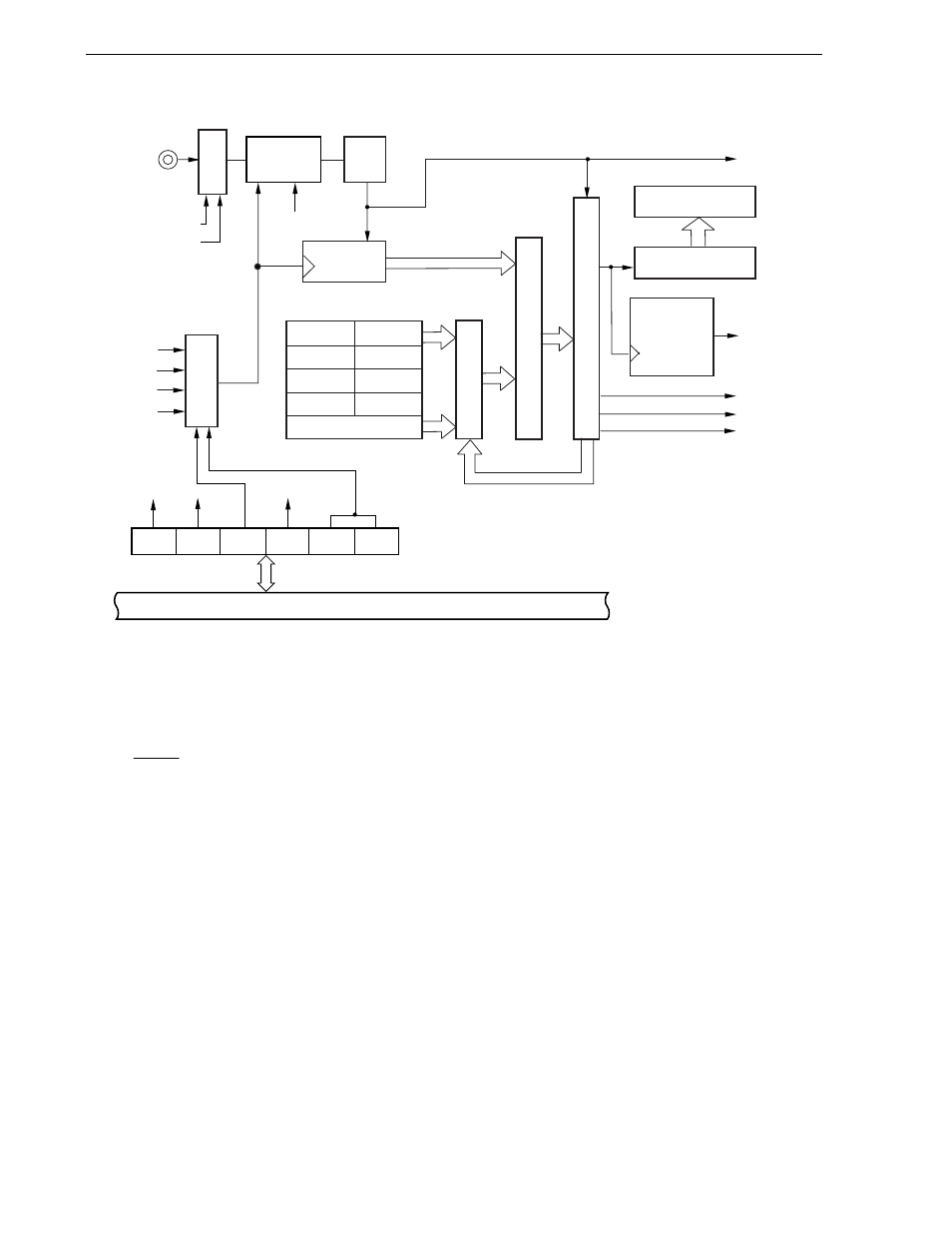

Figure 15-1. Block Diagram of Remote Controller Receiver

RIN/P34

Noise

canceler

f

X

/2

6

f

X

/2

7

f

X

/2

8

f

XT

Clock

counter

Selector

Remote controller receive control register (

RMCN)

Internal bus

RMIN

PRSEN

RMCK1 RMCK0

Input control

Edge

detection

Compare register

RMGPHS

RMGPHL

RMDLS

RMDLL

RMDH0S

RMDH0L

RMDH1S

RMDH1L

NCW

RMEN

Register selection

Comparator

Data detection

Selection control

signal

Remote

controller shift

register receive

counter register

(RMSCR)

INTDFULL

Remote controller receive

shift register (RMSR)

Remote controller receive

data register (RMDR)

INTRERR

INTREND

INTGP

INTRIN

RMIN

RMEN

NCW

End-width select register (RMER)

(1) Remote controller receive shift register (RMSR)

This is an 8-bit register for reception of remote controller data.

Data is stored in bit 7 first. Each time new data is stored, the stored data is shifted to the lower bits. Therefore,

the latest data is stored in bit 7, and the first data is stored in bit 0.

RMSR is read with an 8-bit memory manipulation instruction.

RESET input sets RMSR to 00H.

Also, RMSR is cleared to 00H under any of the following conditions.

• Remote controller stops operation (RMEN = 0).

• Error is detected (INTRERR is generated).

• INTDFULL is generated.

• RMSR is read after INTREND has been generated.

Caution Reading RMSR is disabled during remote controller reception. Complete reception, then

read RMSR. When the reading operation is complete, RMSR is cleared. Therefore, values

once read are not guaranteed.