NEC PD78F9488 User Manual

Page 387

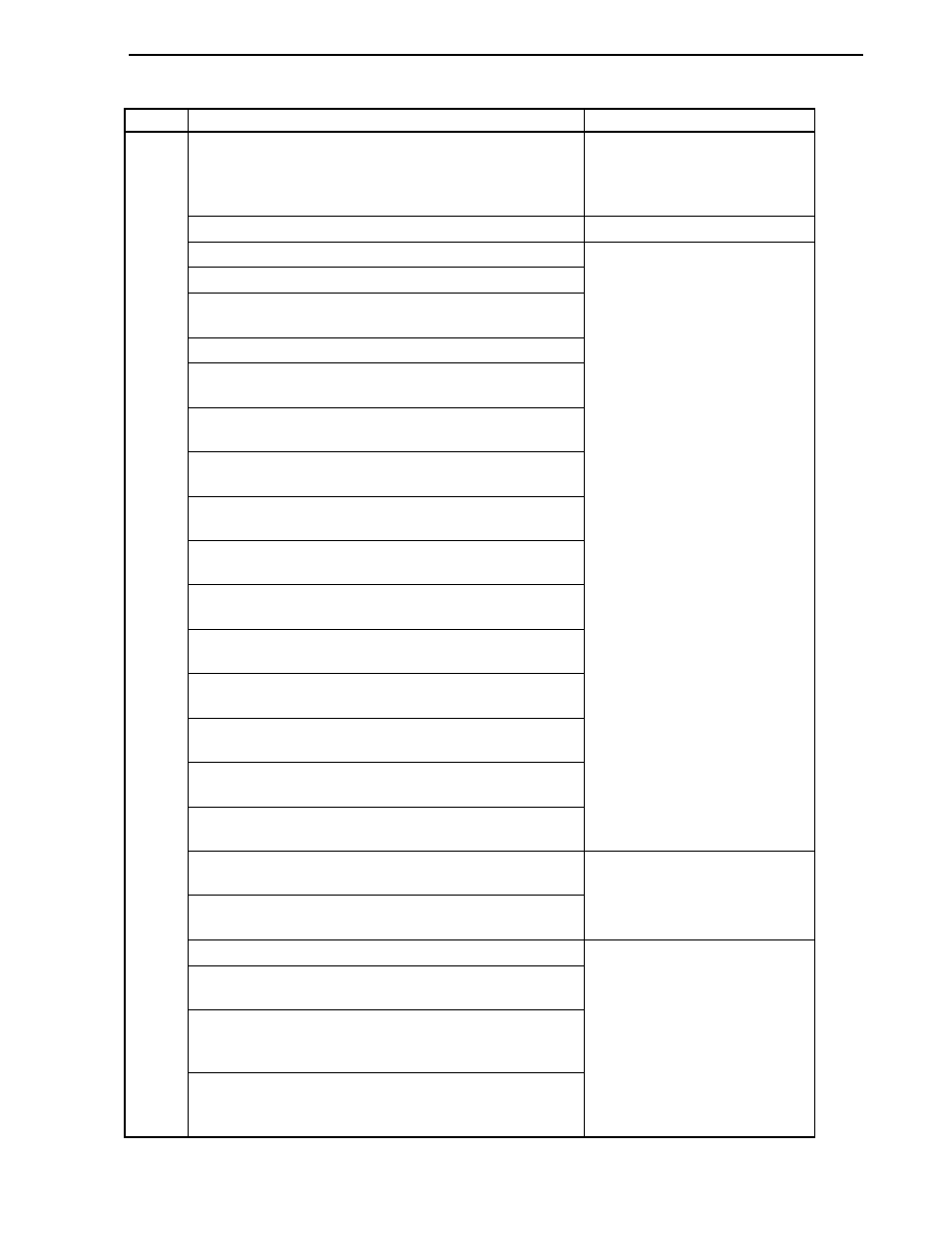

APPENDIX D REVISION HISTORY

User’s Manual U15331EJ4V1UD

387

(3/4)

Edition

Major Revision from Previous Edition

Applied to:

Change of descriptions of

µ

PD789489, 78F9489

• Change of status from under development to development

completed

• Change of the subseries name to “

µ

PD789489 subseries”

Throughout

Update of 1.5 78K/0S Series Lineup to latest version

CHAPTER 1 GENERAL

Modification of Figure 7-2 Block Diagram of Timer 50

Modification of Figure 7-3 Block Diagram of Timer 60

Modification of Figure 7-5 Block Diagram of Output control

circuit (Timer 60)

Addition of descriptions in 7.2 (2) 8-bit compare register 60

Addition of descriptions in 7.2 (4) 8-bit H width compare registers

60 and 61

Modification of Figure 7-11 8-bit Timing of Interval Timer

Operation with 8-Bit Resolution (Basic Operation)

Modification of Figure 7-13. Timing of Interval Timer Operation

with 8-Bit Resolution (When CRnm Is Set to FFH)

Modification of Figure 7-17. Timing of Operation of External

Event Counter with 8-Bit Resolution

Addition of descriptions of setting sequence in 7.4.3 Operation as

carrier generator

Modification of Figure 7-22. Timing of Carrier Generator

Operation (When CR60 = N, CRH60 = M (M > N))

Modification of Figure 7-23. Timing of Carrier Generator

Operation (When CR60 = N, CRH60 = M (M < N))

Modification of Figure 7-24. Timing of Carrier Generator

Operation (When CR60 = CRH60 = N)

Modification of the mode name in 7.4.4 PWM output mode

operation (timer 50)

Modification of the mode name in 7.4.5 PPG output mode

operation (timer 60 and 61)

Modification of (1) Error on starting timer in 7.5 Cautions on

Using 8-Bit Timers 50, 60, and 61

CHAPTER 7 8-BIT TIMERS 50, 60,

61

Modification of Figure 10-1. Block Diagram of 10-bit A/D

converter

Modification of (1) Current consumption in standby mode in 10.5

Cautions Related to 10-Bit A/D Converter

CHAPTER 10 10-BIT A/D

CONVERTER

Modification of Figure 11-1. Block Diagram of Serial Interface 20

Addition of Caution in Figure 11-3 Format of Serial Operation

Mode Register 20

Addition of descriptions about remote controller receiver and key

return signal detection pin in Figure 11-6 Format of Baud Rate

Generator Control Register 20

4th

Modification of descriptions about CPU Clock in Table 11-3 and

11-5. Example of Relationship Between System Clock and

Baud Rate

CHAPTER 11 SERIAL INTERFACE

20