NEC PD78F9488 User Manual

Page 100

CHAPTER 5 CLOCK GENERATOR

100

User’s Manual U15331EJ4V1UD

(4) Subclock selection register (SSCK) (

µPD78F9488, 78F9489 only)

This register is used to control the operation of the

×4 subsystem clock multiplication circuit.

SSCK is set via a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to 00H.

Caution This register is valid only in the

µPD78F9488 and 78F9489; however, writing to it in the

µPD789488 and 789489 will simply make it invalid, causing no operational effect.

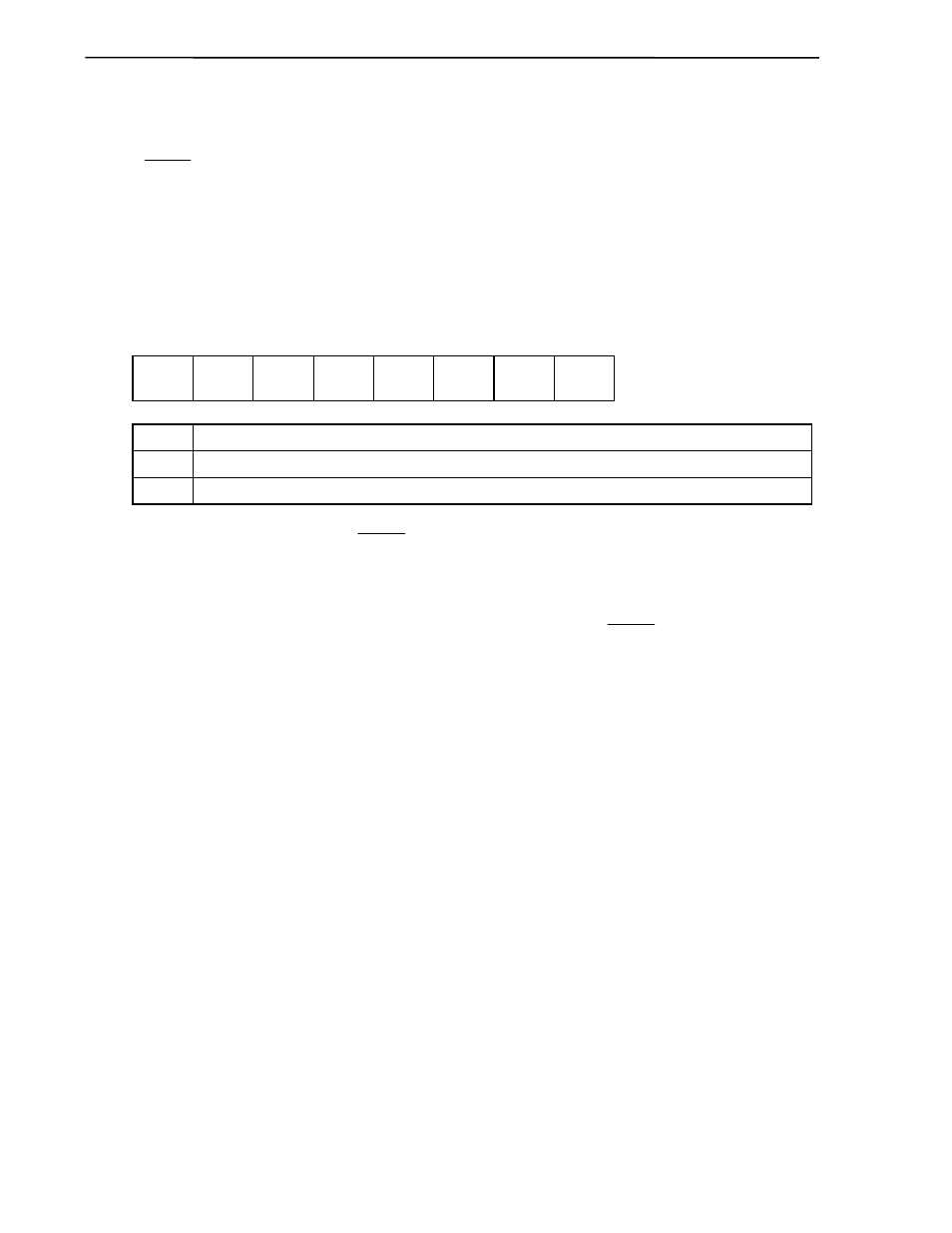

Figure 5-6. Subclock Selection Register Format

Symbol

7 6 5 4 3 2 1 0

Address

After

reset

R/W

SSCK

0 0 0 0 0 0 0

SCT

FF46H

Retained

Not

e

R/W

SCT

Control

of

×4 subsystem clock multiplication circuit

0

Operation stopped (subsystem clock source (32.768 kHz) supplied to the CPU)

1

Operation enabled (clock that is the subsystem clock multiplied by 8 (262 kHz) supplied to the CPU)

Note The register is set to 00H only by RESET input.

Cautions 1. Always set bits 1 to 7 to 0.

2. Write to the SCT flag prior to setting the CSS0 flag to 1 following the release of reset. Write

operations following the first operation are invalid (input the RESET signal to rewrite).