NEC PD78F9488 User Manual

Page 126

CHAPTER 7 8-BIT TIMERS 50, 60, AND 61

User’s Manual U15331EJ4V1UD

126

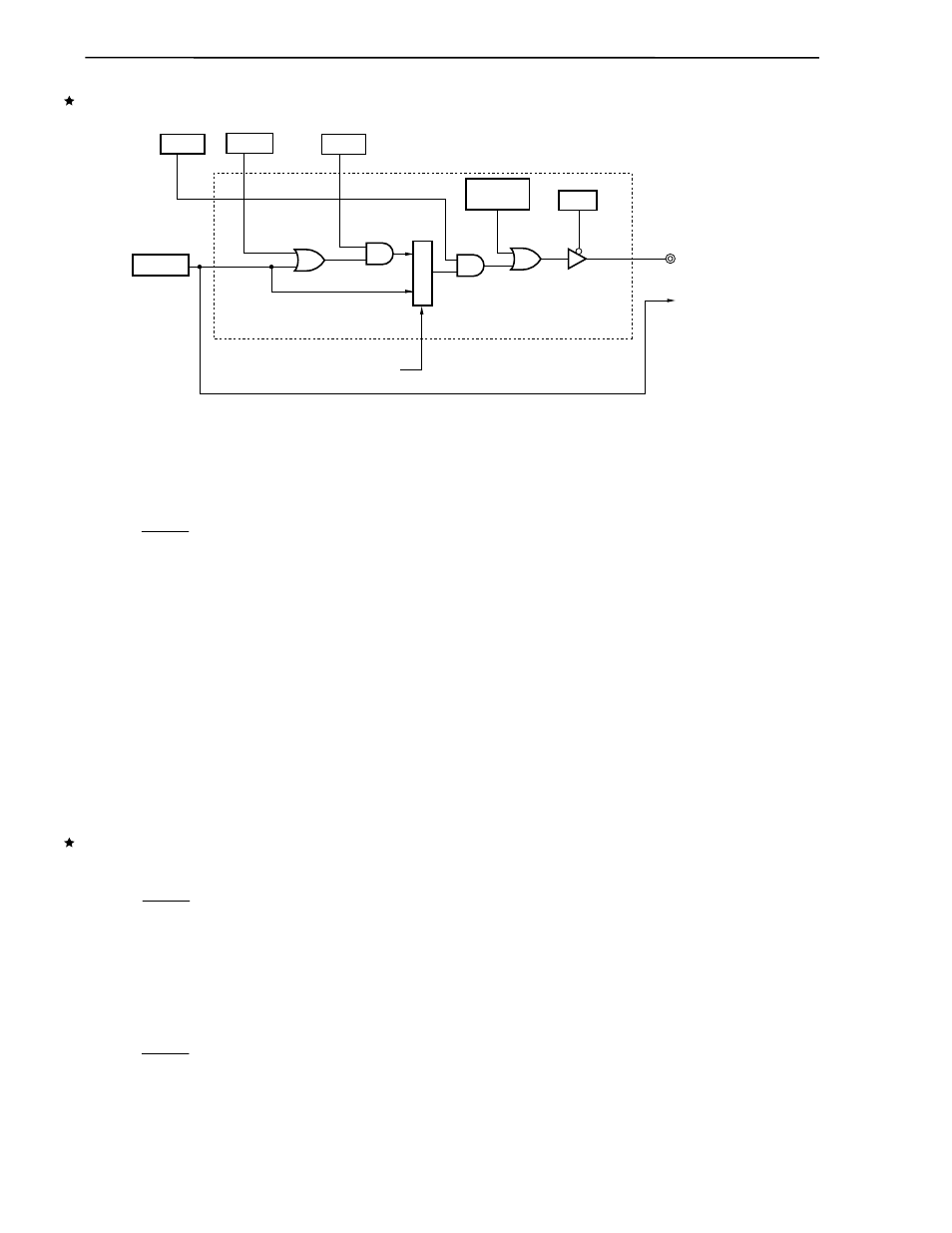

Figure 7-5. Block Diagram of Output Controller (Timer 60)

F/F

RMC60

NRZ60

TOE60

PM31

P31

output latch

Selector

TO60/INTP1/P31

Carrier generator mode

Carrier clock

(1) 8-bit compare register 50 (CR50)

This 8-bit register is used to continually compare the value set to CR50 with the count value in 8-bit timer

counter 50 (TM50) and to issue an interrupt request (INTTM50) when a match occurs. In PWM mode, this

register is used for high-level width setting.

CR50 is set with an 8-bit memory manipulation instruction.

RESET input makes this register undefined.

Cautions 1. In PWM output mode (TMD501 = 1, TMD500 = 0), if CR50 is rewritten while the timer is

operating, a high level may be output for one clock cycle immediately after this rewrite

operation. If this waveform may cause problems in the application, either <1> stop the

timer when rewriting CR50, or <2> rewrite CR50 after TOE50 has been cleared.

2. If both edges have been selected as the valid edge of the count clock in PWM output

mode (TEG50 = 1), do not set CR50 to 00H, 01H, or FFH. Also, if the rising edge has

been selected as the valid edge (TEG50 = 0), do not set CR50 to 00H.

(2) 8-bit compare register 60 (CR60)

When connected to TM50 via a cascade connection and using as a 16-bit timer/event counter, the interrupt

request (INTTM60) occurs only when matches occur simultaneously between CR50 and TM50 and between

CR60 and TM60 (INTTM50 is not generated).

In carrier generator mode and PPG output mode, the low-level width of timer output is set by writing a value

to CR60.

CR60 is set with an 8-bit memory manipulation instruction.

RESET input makes this register undefined.

(3) 8-bit compare register 61 (CR61)

This 8-bit register is used to continually compare the value set to CR61 with the count value in 8-bit timer

counter 61 (TM61) and issue an interrupt request (INTTM61) when a match occurs. In PPG output mode,

this registered used for low-level width setting.

CR61 is set with an 8-bit memory manipulation instruction.

RESET input makes this register undefined.