NEC PD78F9488 User Manual

Page 170

CHAPTER 9 WATCHDOG TIMER

170

User’s Manual U15331EJ4V1UD

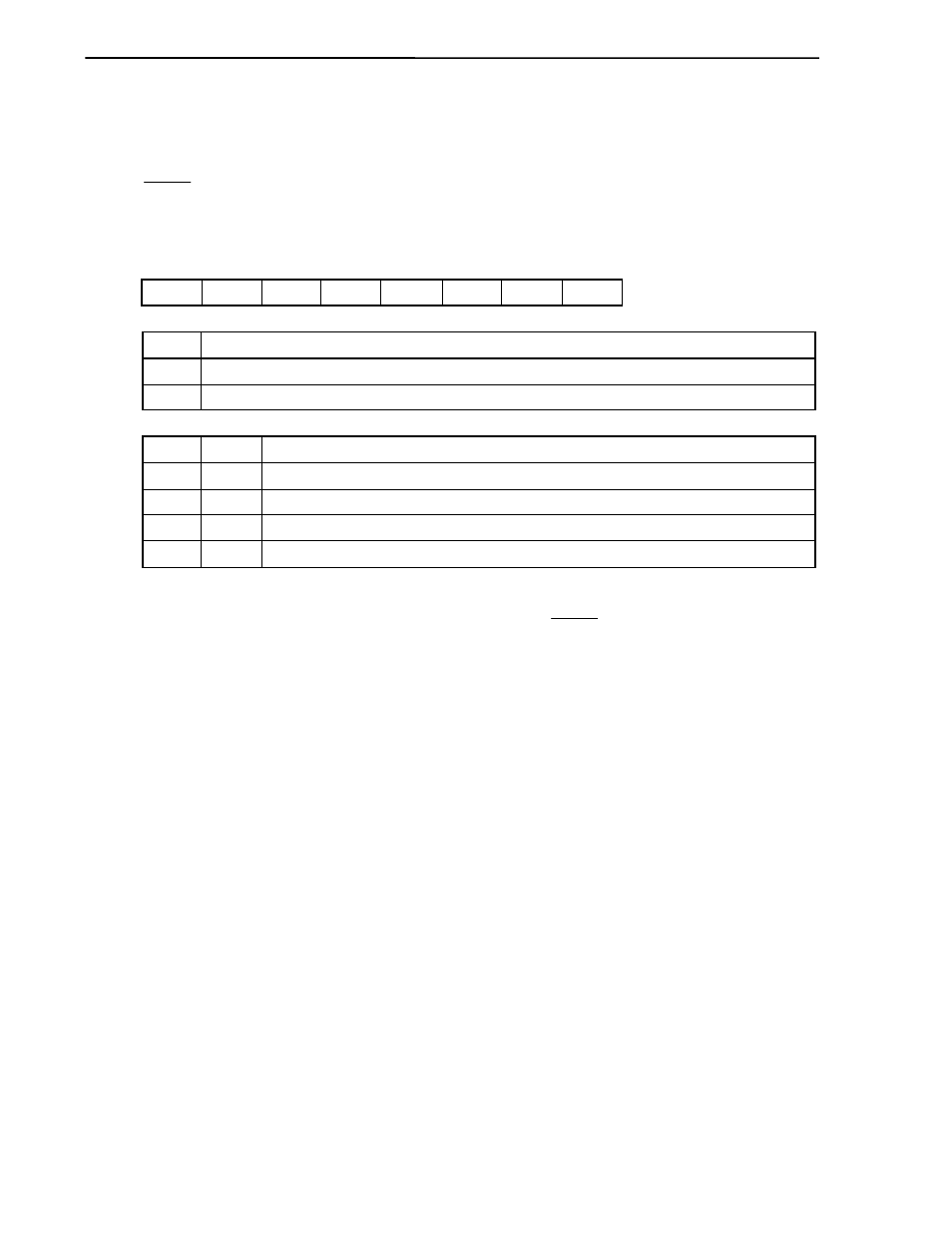

(2) Watchdog timer mode register (WDTM)

This register sets the operation mode of the watchdog timer, and enables/disables counting of the watchdog

timer.

WDTM is set with a 1-bit or 8-bit memory manipulation instruction.

RESET input sets WDTM to 00H.

Figure 9-3. Format of Watchdog Timer Mode Register

RUN

0

1

Watchdog timer operation selection

Note 1

Stop counting.

Clear counter and start counting.

WDTM4

Watchdog timer operation mode selection

Note 2

WDTM3

0

1

1

0

1

1

Operation stop

Interval timer mode (a maskable interrupt is generated upon overflow occurrence)

Note 3

Watchdog timer mode 1 (a non-maskable interrupt is generated upon overflow occurrence)

Watchdog timer mode 2 (a reset operation is started upon overflow occurrence)

0

0

RUN

0

0

WDTM4

WDTM3

0

0

0

WDTM

<7>

6

5

4

Symbol

Address

After reset

R/W

FFF9H

00H

R/W

3

2

1

0

Notes 1. Once RUN has been set (1), it cannot be cleared (0) by software. Therefore, when counting is

started, it cannot be stopped by any means other than RESET input.

2. Once WDTM3 and WDTM4 have been set (1), they cannot be cleared (0) by software.

3. The watchdog timer starts operation as an interval timer when RUN is set to 1.

Cautions 1. When the watchdog timer is cleared by setting RUN to 1, the actual overflow time is up

to 0.8% shorter than the time set by the watchdog timer clock selection register (WDCS).

2. To set watchdog timer mode 1 or 2, set WDTM4 to 1 after confirming WDTIF (bit 0 of

interrupt request flag register 0 (IF0)) is set to 0. When watchdog timer mode 1 or 2 is

selected with WDTIF set to 1, a non-maskable interrupt is generated upon the

completion of rewriting WDTM4.