NEC PD78F9488 User Manual

Page 202

CHAPTER 11 SERIAL INTERFACE 20

202

User’s Manual U15331EJ4V1UD

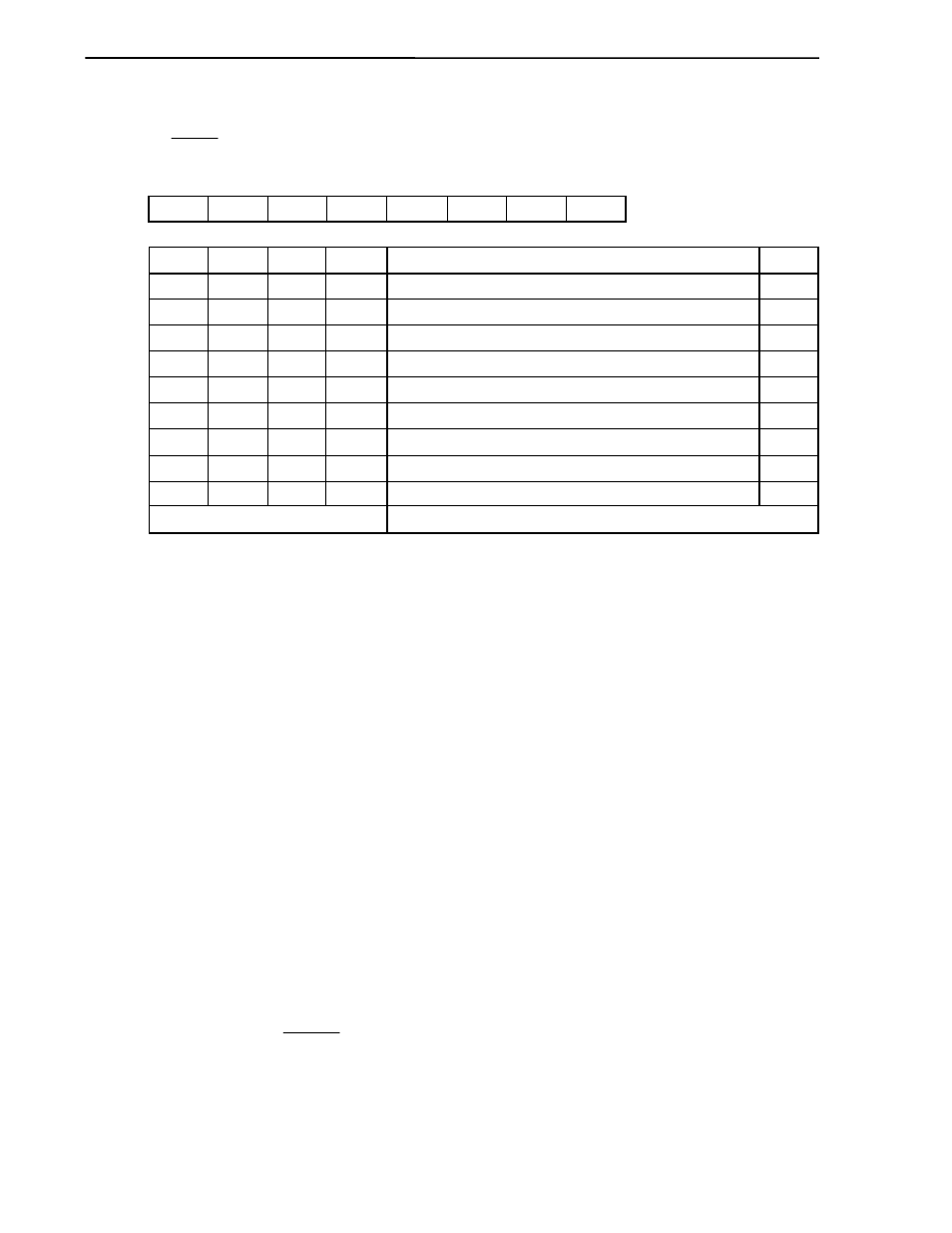

(d) Baud rate generator control register 20 (BRGC20)

BRGC20 is set with an 8-bit memory manipulation instruction.

RESET input sets BRGC20 to 00H.

TPS203

0

0

0

0

0

0

0

0

1

TPS202

0

0

0

0

1

1

1

1

0

f

X

/2

f

X

/2

2

f

X

/2

3

f

X

/2

4

f

X

/2

5

f

X

/2

6

f

X

/2

7

f

X

/2

8

(2.5 MHz)

(1.25 MHz)

(625 kHz)

(313 kHz)

(156 kHz)

(78.1 kHz)

(39.1 kHz)

(19.5 kHz)

TPS201

0

0

1

1

0

0

1

1

0

TPS200

0

1

0

1

0

1

0

1

0

n

1

2

3

4

5

6

7

8

−

Setting prohibited

Selection of baud rate generator source clock

External clock input to ASCK20 pin

Note

Other than above

TPS203

TPS202

TPS201

TPS200

0

0

0

0

BRGC20

7

6

5

4

Symbol

Address

After reset

R/W

FF73H

00H

R/W

3

2

1

0

Note Can only be used in the UART mode.

Cautions 1. When writing to BRGC20 during a communication operation, the output of the baud

rate generator is disrupted and communications cannot be performed normally. Be

sure not to write to BRGC20 during a communication operation.

2. Be sure not to select n = 1 during operation at f

X

> 2.5 MHz because the resulting

baud rate exceeds the rated range.

3. When the external input clock is selected, set input mode by setting bit 0 of port

mode register 2 (PM2) to 1.

Remarks 1. f

X

: Main system clock oscillation frequency

2. n: Values determined by the settings of TPS200 to TPS203 (1

≤ n ≤ 8)

3. The parenthesized values apply to operation at f

X

= 5.0 MHz.

The baud rate transmit/receive clock to be generated is either a divided system clock signal, or a signal

obtained by dividing the clock input to the ASCK20 pin.

(i) Generation of baud rate transmit/receive clock from system clock

The transmit/receive clock is generated by dividing the system clock. The baud rate of a clock

generated from the system clock is estimated by using the following expression.

[Baud rate] = [bps]

f

X

: Main system clock oscillation frequency

n: Values in the above table determined by the settings of TPS200 to TPS203 (2

≤ n ≤ 8)

f

X

2

n + 1

Ч 8