NEC PD78F9488 User Manual

Page 249

CHAPTER 12 SERIAL INTERFACE 1A0

User’s Manual U15331EJ4V1UD

249

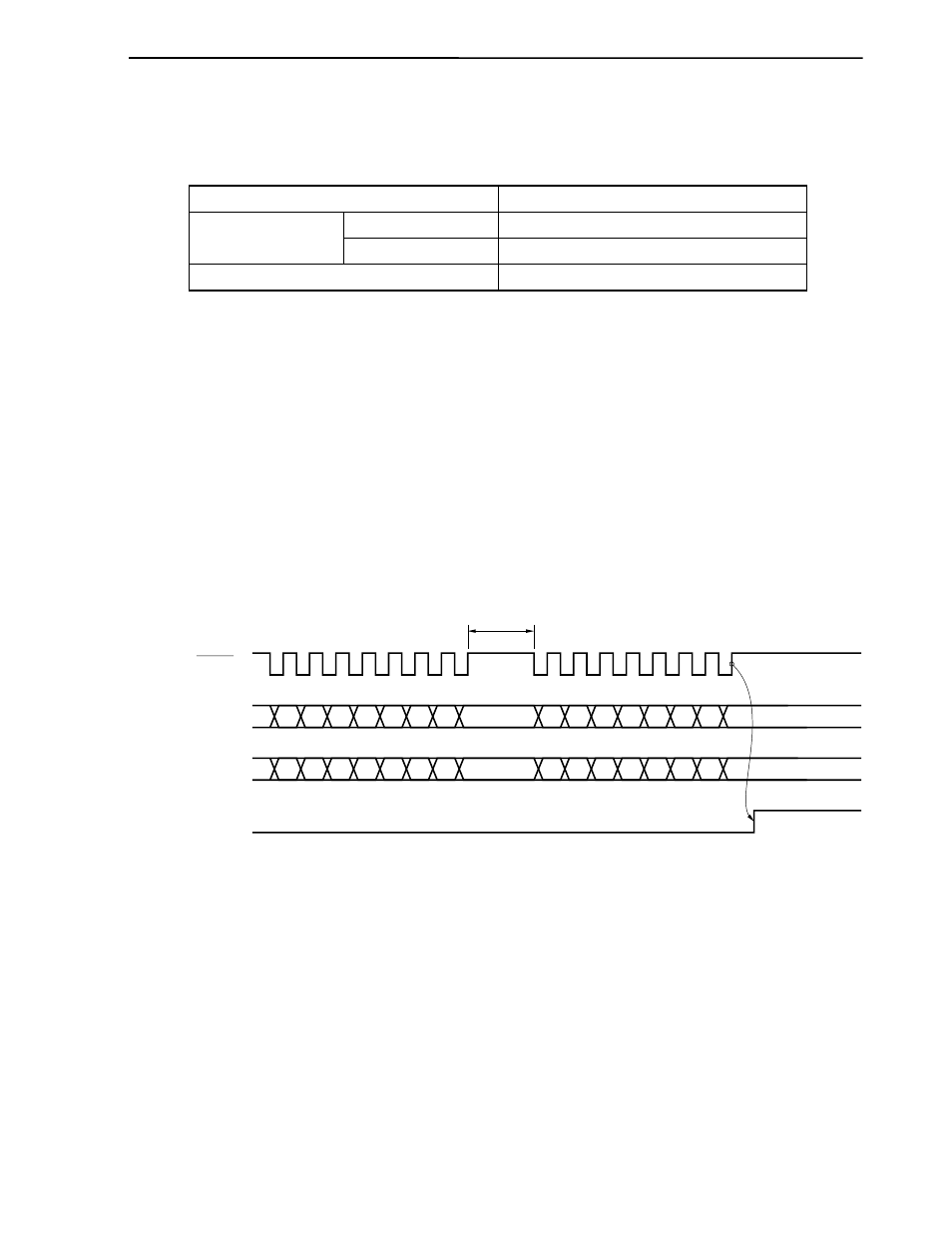

(4) Timing of interrupt request signal generation

The interrupt request signal is generated in synchronization with the timing shown in Table 12-2.

Table 12-2. Timing of Interrupt Request Signal Generation

Operation Mode

Timing of Interrupt Request Signal

Master mode

10th serial clock at end of transfer

Single mode

Slave mode

8th serial clock at end of transfer

Repeat transmit mode

Not generated

(5) Interval time of automatic transmission/reception

Because read/write to/from the buffer RAM using the automatic transmit/receive function is performed

asynchronously to the CPU processing, the interval time is dependent on the CPU processing of the timing of

the eighth rising of the serial clock and the set value of automatic data transmit/receive interval specification

register 0 (ADTI0). Whether the interval time is dependent on ADTI0 is selected by setting bit 7 (ADTI07) of

ADTI0. If ADTI07 is reset to 0, the interval time is 2/f

SCK

. If ADTI07 is set to 1, whichever is greater of the

interval time determined by the set contents of ADTI0 or the interval time (2/f

SCK

) determined by the CPU

processing is selected.

Figure 12-17 shows the interval time of automatic transmission/reception.

Remark f

SCK

: Serial clock frequency

Figure 12-17. Interval Time of Automatic Transmission/Reception

Interval

SCK10

D7

SO10

SI10

CSIIF10

D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0

The following expression must be satisfied to access the buffer RAM.

1 transfer cycle + Interval time

≥ Read access + Write access + CPU buffer RAM access (time)

In the case of a “high-speed CPU & low-speed SCK”, the interval time is not necessary. In the case of a

“low-speed CPU & high-speed SCK”, the interval time is necessary.

In this case, make sure that a sufficient interval time elapses, by using automatic data transmit/receive

interval specification register 0 (ADTI0), so that the above expression is satisfied.