NEC PD78F9488 User Manual

Page 386

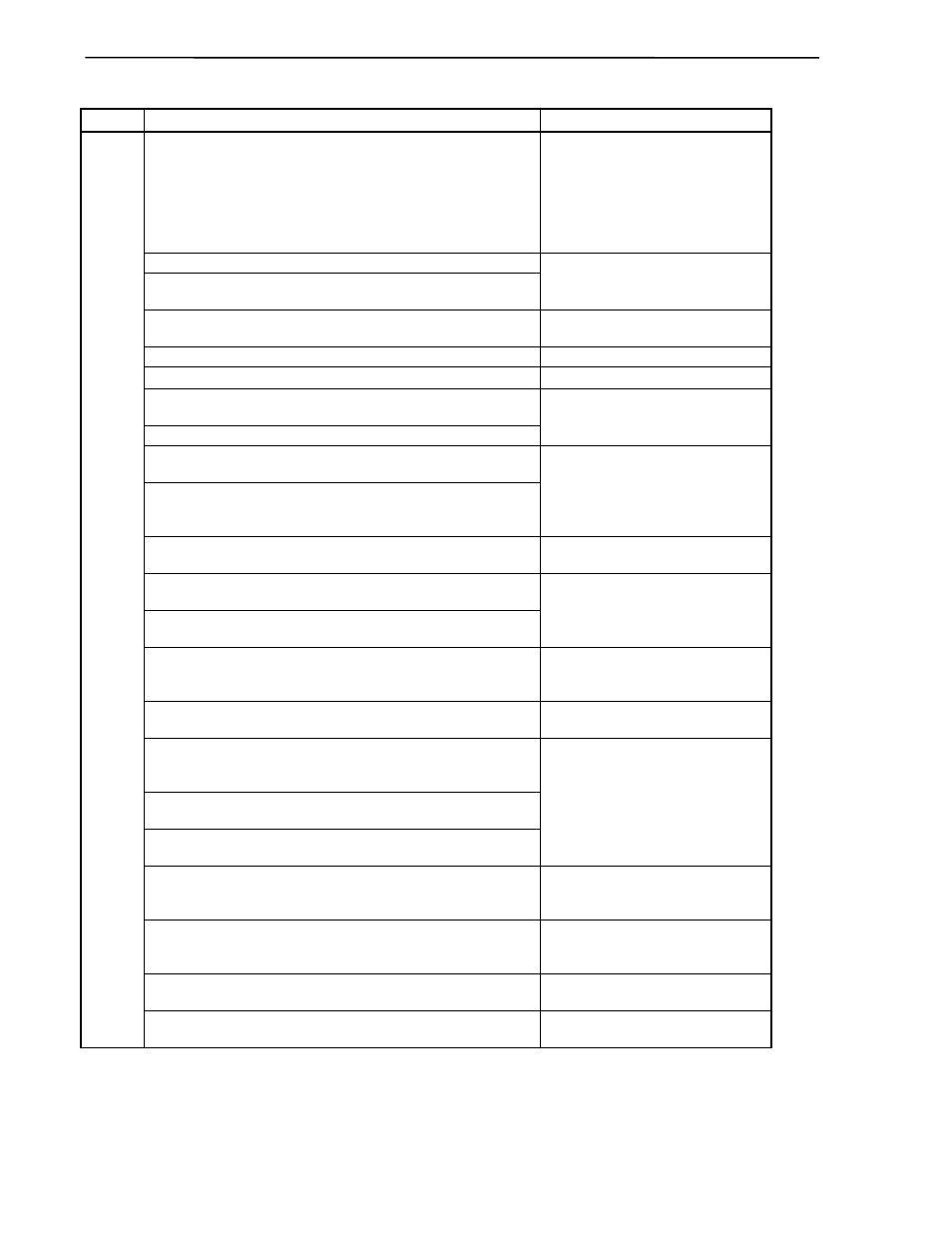

APPENDIX D REVISION HISTORY

User’s Manual U15331EJ4V1UD

386

(2/4)

Edition

Major Revision from Previous Edition

Applied to:

Addition of descriptions of

µ

PD789489, 78F9489 (under

development)

• Key return detection function added to port 6 (

µ

PD789489,

78F9489 only)

• Key return pin name of port 0 changed (

µ

PD789489, 78F9489

only)

• Remote controller receiver added (

µ

PD789489, 78F9489 only)

Throughout

Addition of description in 2.2.20 V

PP

(Flash Memory Version Only)

Addition of description about AV

DD

, AV

SS

in Table 2-1 Types of Pin

I/O Circuits

CHAPTER 2 PIN FUNCTIONS

Addition of internal low-speed RAM to 3.1.2 Internal data memory

space

CHAPTER 3 CPU ARCHITECTURE

Modification of Figure 4-2 Block Diagram of P00 to P07

CHAPTER 4 PORT FUNCTIONS

Addition of 5.4.6 Subsystem clock

×4 multiplication circuit

CHAPTER 5 CLOCK GENERATOR

Modification of descriptions in 6.4.1 Operation as timer interrupt

and 6.4.2 Operation as timer output

Addition of 6.5 Cautions on 16-bit timer 20

CHAPTER 6 16-BIT TIMER 20

Correction of maximum intervals in Table 7-4 Interval Time of

Timer 60 and Table 7-5 Interval Time of Timer 61

Correction of maximum pulse widths in Table 7-7 Square-Wave

Output Range of Timer 60 and Table 7-8 Square-Wave Output

Range of Timer 61

CHAPTER 7 8-BIT TIMERS 50, 60,

61

Modification of Caution in Figure 8-4 Watch Timer/Interval Timer

Operation Timing

CHAPTER 8 WATCH TIMER

Addition of descriptions in (2) A/D conversion result register 0

(ADCRL0) in 10.2 10-Bit A/D Converter Configuration

Addition of (8) Input impedance of ANI0 to ANI7 pins in 10.5

Cautions Related to 10-Bit A/D Converter

CHAPTER 10 10-BIT A/D

CONVERTER

Addition of the remote controller receiver chapter

CHAPTER 15 REMOTE

CONTROLLER RECEIVER

(

µ

PD789489, 78F9489 ONLY)

Modification of Caution in Figure 16-6 Format of Key Return

Mode Register 00

CHAPTER 16 INTERRUPT

FUNCTIONS

Addition of descriptions about remote controller receiver and key

return signal detection pin in Table 19-1 Difference Between

µPD78F9488, 78F9489, and Mask ROM Version

Modification of descriptions about CPU Clock in Table 19-2

Communication Mode List

Modification of Notes in Figure 19-3 Example of connection with

Dedicated Flash Programmer

CHAPTER 19 FLASH MEMORY

VERSION

Addition of Note to Absolute Maximum Ratings

CHAPTER 22 ELECTRICAL

SPECIFICATIONS (

µ

PD789488,

78F9488)

Addition of electrical specifications of

µ

PD789489, 78F9489

(target)

CHAPTER 23 ELECTRICAL

SPECIFICATIONS (TARGET)

(

µ

PD789489, 78F9489)

Modification of A.5 Debugging Tools (Hardware)

APPENDIX A DEVELOPMENT

TOOLS

3rd

Addition of cautions on designing target system

APPENDIX B NOTES ON TARGET

SYSTEM DESIGN