NEC PD78F9488 User Manual

Page 299

CHAPTER 16 INTERRUPT FUNCTIONS

User’s Manual U15331EJ4V1UD

299

(5) Key return mode register 00 (KRM00)

This register is used to set the pin that is to detect the key return signal (rising edge of port 0).

KRM00 is set with a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to 00H.

Figure 16-6. Format of Key Return Mode Register 00

Symbol

7 6 5 4 3 2 1 0

Address

After

reset

R/W

KRM00 KRM007 KRM006 KRM005 KRM004

0

0

0

KRM000

FFF5H

00H

R/W

KRM000

Control of key return signal detection

0

Key return signal not detected

1

Key return signal detected (P00 to P03 falling edge detection)

KRM00n

Control of key return signal detection

0

Key return signal not detected

1

Key return signal detected (P0n falling edge detection)

Remark n = 4 to 7

Cautions 1. Always set bits 1 to 3 to 0.

2. Before setting KRM00, set (1) bit 0 (KRMK00) of MK2 to disable interrupts. To enable

interrupts, clear (0) KRMK00 after clearing (0) bit 0 (KRIF00) of IF2.

3. On-chip pull-up resistors are not automatically connected in input mode even when key

return signal detection is specified. Therefore, when detecting the key return signal,

connect the pull-up resistor of the corresponding bit using pull-up resistor option

register B0 (PUB0). Although these resistors are disconnected when the mode changes

to output, key return signal detection continues unchanged.

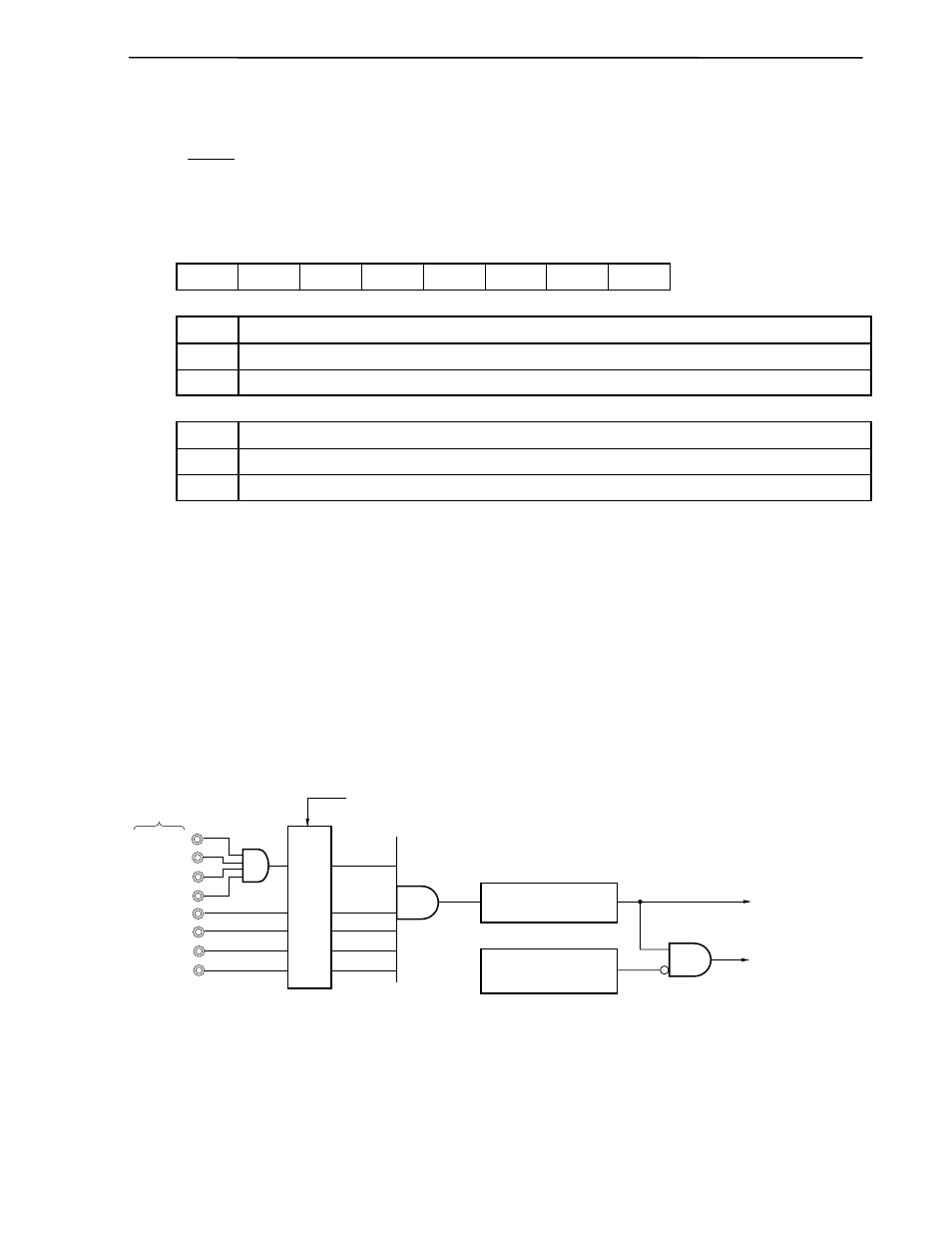

Figure 16-7. Block Diagram of Falling Edge Detector

P00/KR0

P01/KR1

P02/KR2

P03/KR3

P04/KR4

P05/KR5

P06/KR6

P07/KR7

Falling edge detector

KRMK00

INTKR00

Standby release

signal

Key return mode register 00

(KRM00)

Selector

Note 2

Note 1

Notes 1. The pin names one P00/KR00 to P07/KR07 in the

µPD789489 and 78F9489.

2. For selecting the pin to be used as falling edge input.