Examples – Altera DDR SDRAM Controller User Manual

Page 91

A–13

Examples

© March 2009

Altera Corporation

DDR and DDR2 SDRAM Controller Compiler User Guide

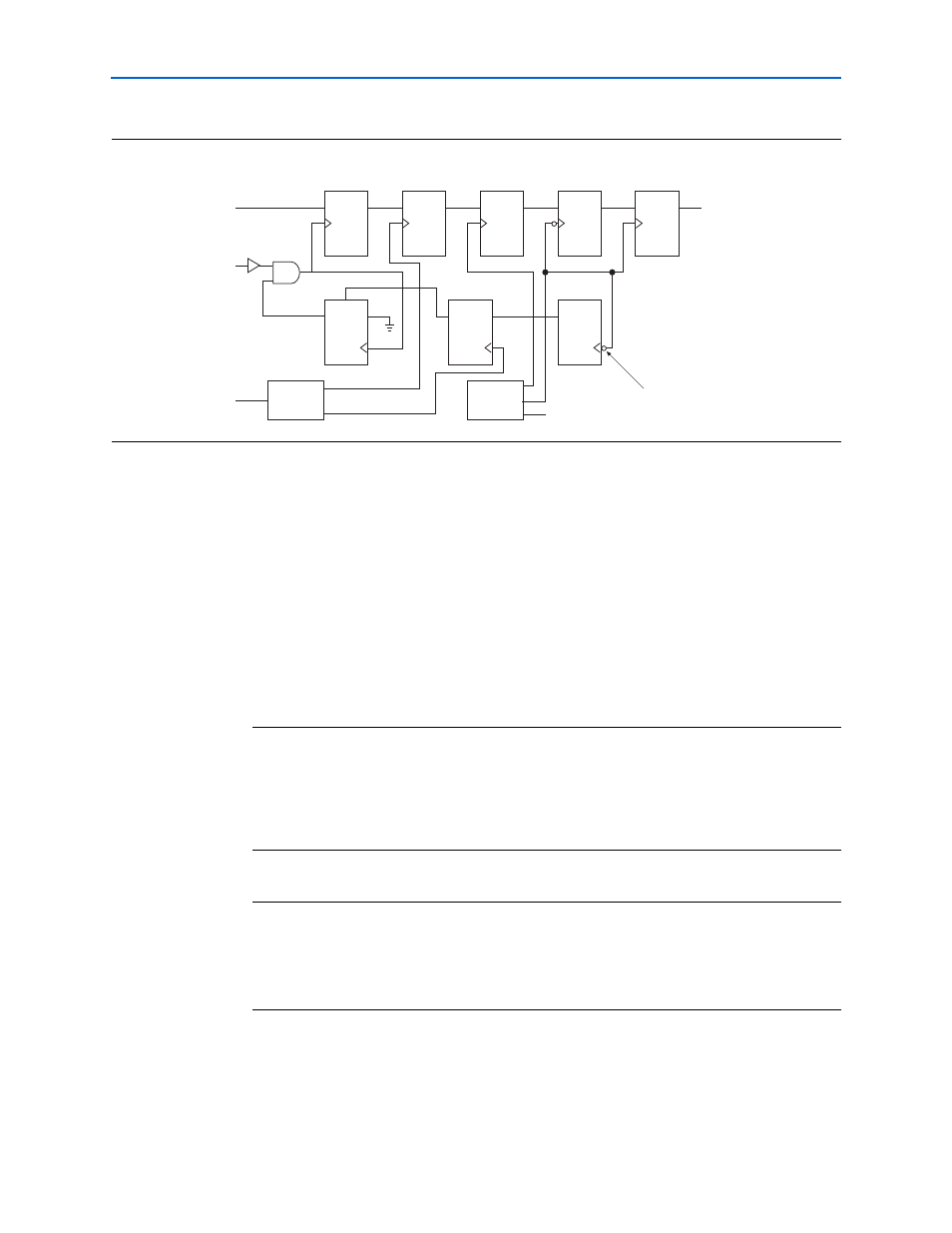

Examples

show the generated PLLs and the PLL outputs for the

following options:

■

Use fedback clock = On

■

Manual resynchronization control = On

■

Resynchronization clock setting = Dedicated

■

Manual postamble control = On

■

Postamble clock setting = Dedicated

Figure A–10. Inserting an Intermediate Postamble Register

D

Q

Q

D

Q

D

Q

D

D

Q

D

Q

D

Q

D

Q

Fedback

PLL

dq_capture

inter_rdata

resynched_data

fedback_resynched_data

inter_rdata

dq

dqs

postamble_clk

resynch_clk

clk

Fedback

Clock Input

System

PLL

Present when

Intermediate Postamble

Register is On

Example A–1. System PLL and Clock Outputs

ddr_pll_stratixii g_stratixpll_ddr_pll_inst

(

.c0 (clk),

.c1 (write_clk),

.c2 (dedicated_resynch_or_capture_clk),

.inclk0 (clock_source)

);

Example A–2. Fedback PLL and Clock Outputs

ddr_pll_fb_stratixii g_stratixpll_ddr_fedback_pll_inst

(

.c0 (fedback_resynch_clk),

.c1 (dedicated_postamble_clk),

.inclk0 (fedback_clk_in)

);