Altera DDR SDRAM Controller User Manual

Page 30

2–20

Chapter 2: Getting Started

MegaWizard Plug-In Manager Design Flow

DDR and DDR2 SDRAM Controller Compiler User Guide

© March 2009

Altera Corporation

4. Set the Tcl variable gRTL_DELAYS to 1, which tells the testbench to model the

extra delays in the system necessary for RTL simulation

5. Load the testbench in your simulator with the timestep set to picoseconds.

VHDL Gate-Level Simulations

For VHDL simulations with gate-level models, follow these steps:

1. Create a directory in the <project directory>\testbench directory.

2. Launch your simulation tool inside this directory and create the following

libraries.

■

<device name>

■

altera

■

auk_ddr_user_lib

3. Compile the files in

into the appropriate library. The files are in VHDL93

format.

4. Set the Tcl variable gRTL_DELAYS to 0, which tells the testbench not to use the

insert extra delays in the system, because these are applied inside the gate-level

model.

5. Load the testbench in your simulator with the timestep set to picoseconds.

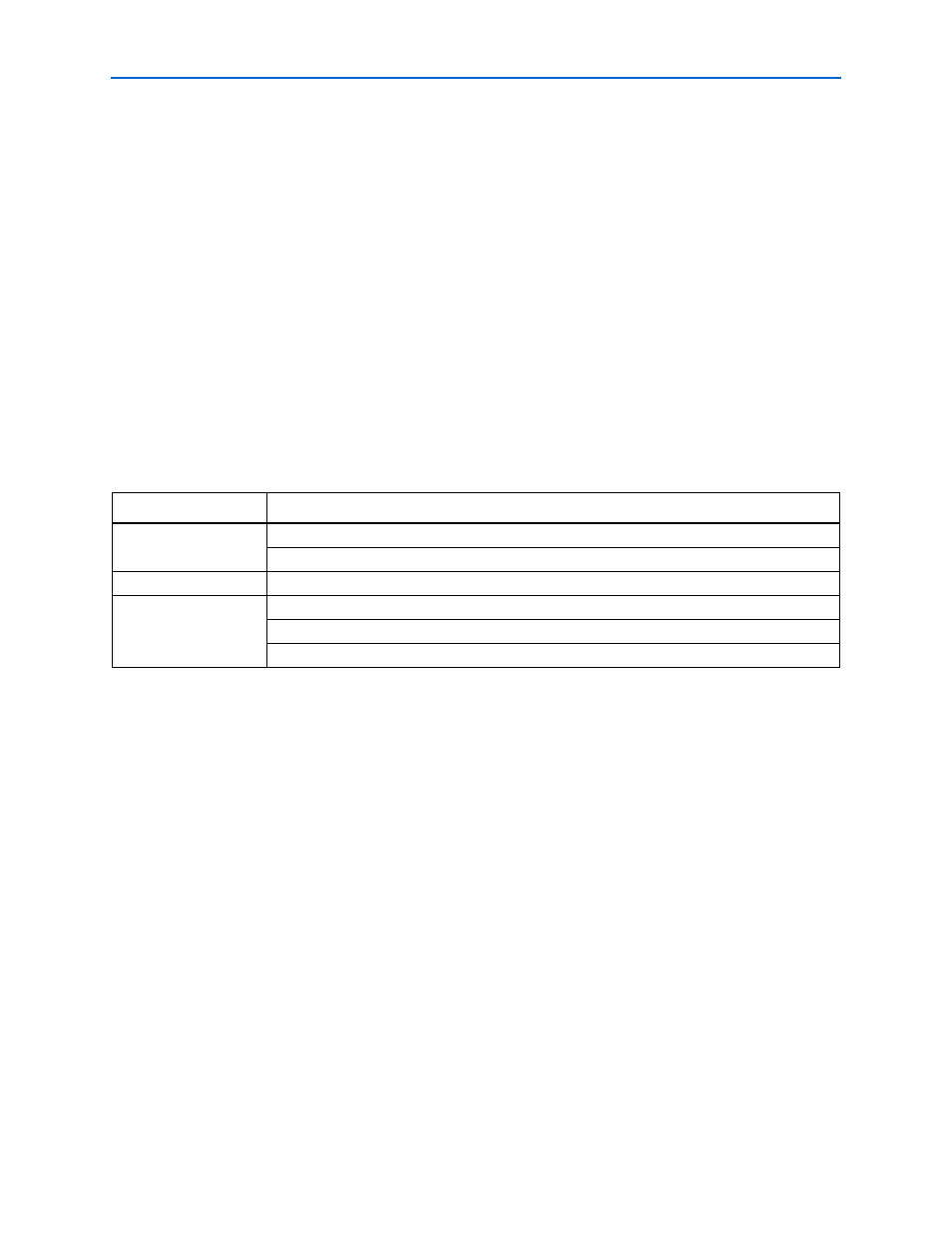

Table 2–3. Files to Compile—VHDL Gate-Level Simulations

Library

Filename

<device name>

<QUARTUS ROOTDIR>/eda/sim_lib/<device name>_atoms.vhd

<QUARTUS ROOTDIR>/eda/sim_lib/<device name>_components.vhd

altera

<QUARTUS ROOTDIR>/libraries/vhdl/altera/altera_europa_support_lib.vhd

auk_ddr_user_lib

<MegaCore install directory>/lib/auk_ddr_tb_functions.vhd

<project directory>/simulation/<simulator name>/<project name>.vho

<project directory>/testbench/<testbench name>.vhd

Notes to

(1) If you are simulating the slow or fast model, the .vho file has a suffix _min or _max added to it. Compile whichever file is appropriate. The

Quartus II software creates models for the simulator you have defined in a directory simulation/<simulator name> in your <project name>

directory..