User refresh control – Altera DDR SDRAM Controller User Manual

Page 60

3–24

Chapter 3: Functional Description

Interfaces & Signals

DDR and DDR2 SDRAM Controller Compiler User Guide

© March 2009

Altera Corporation

2. The user logic requests a write, a read, and another write request, which are

accepted.

3. The controller asserts the write data request signal to ask the user logic to present

valid write data and byte enables on the next clock edge.

4. The read data from the first read request is returned and marked as valid by the

read data valid signal.

5. The controller again asserts the write data request for the second write request.

6. The read data from the second read request is returned.

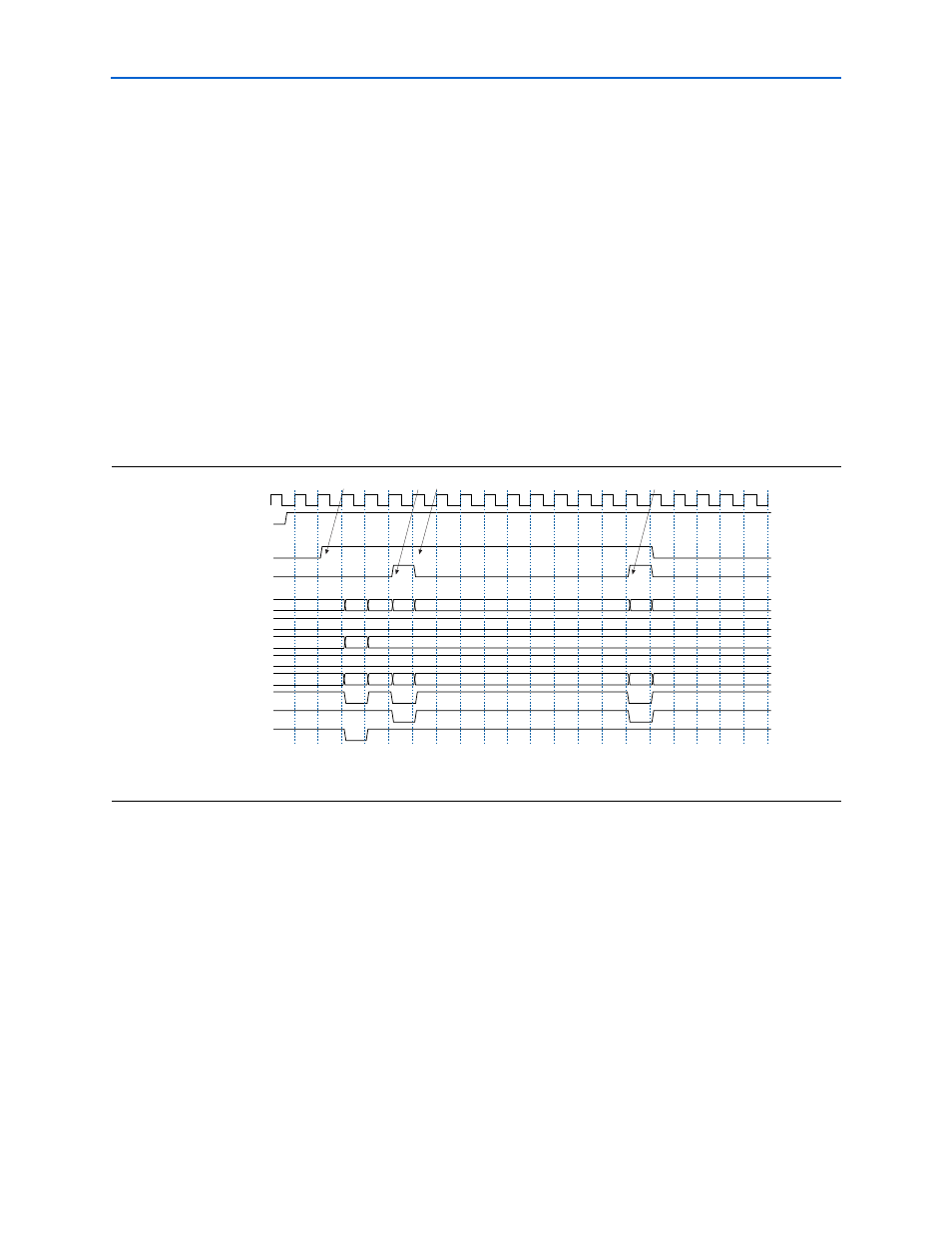

User Refresh Control

shows the user refresh control interface. This feature allows you to control

when the controller issues refreshes to the memory. This feature allows better control

of worst case latency and allows refreshes to be issued in bursts to take advantage of

idle periods.

1. The user logic asserts the refresh request signal to indicate to the controller that it

should perform a refresh. The state of the read and write requests signal does not

matter as the controller gives priority to the refresh request (although it completes

any currently active reads or writes).

2. The controller asserts the refresh acknowledge signal to indicate that it has issued

a refresh. This signal is still available even if the user refresh control option is not

switched on, allowing the user logic to keep track of when the controller is issuing

refreshes.

3. The user logic keeps the refresh request signal asserted to indicate that it wishes to

perform another refresh request.

The controller again asserts the refresh acknowledge signal to indicate that it has

issued a refresh. At this point the user logic deasserts the refresh request signal and

the controller continues with the reads and writes in its buffers.

Figure 3–16. User Refresh Control

Note to

(1) DDR Command shows the command that the command signals are issuing.

clk

reset_n

local_refresh_req

local_refresh_ack

ddr_cs_n

ddr_cke

ddr_a

ddr_ba

DDR Command

ddr_ras_n

ddr_cas_n

ddr_we_n

FF

00

FF

00

FF

00

FF

00

FF

0000

0400

0000

0400

0

NOP

PCH NOP ARF

NOP

ARF

NOP

ARF

DDR SDRAM Interface

Local Interface

[1]

[2]

[4]

[3]