Project settings, Project settings –40, Project settings” on – Altera DDR SDRAM Controller User Manual

Page 76

3–40

Chapter 3: Functional Description

Parameters

DDR and DDR2 SDRAM Controller Compiler User Guide

© March 2009

Altera Corporation

Project Settings

shows the example design options.

shows the variation path options.

shows the device pin prefixes and names options.

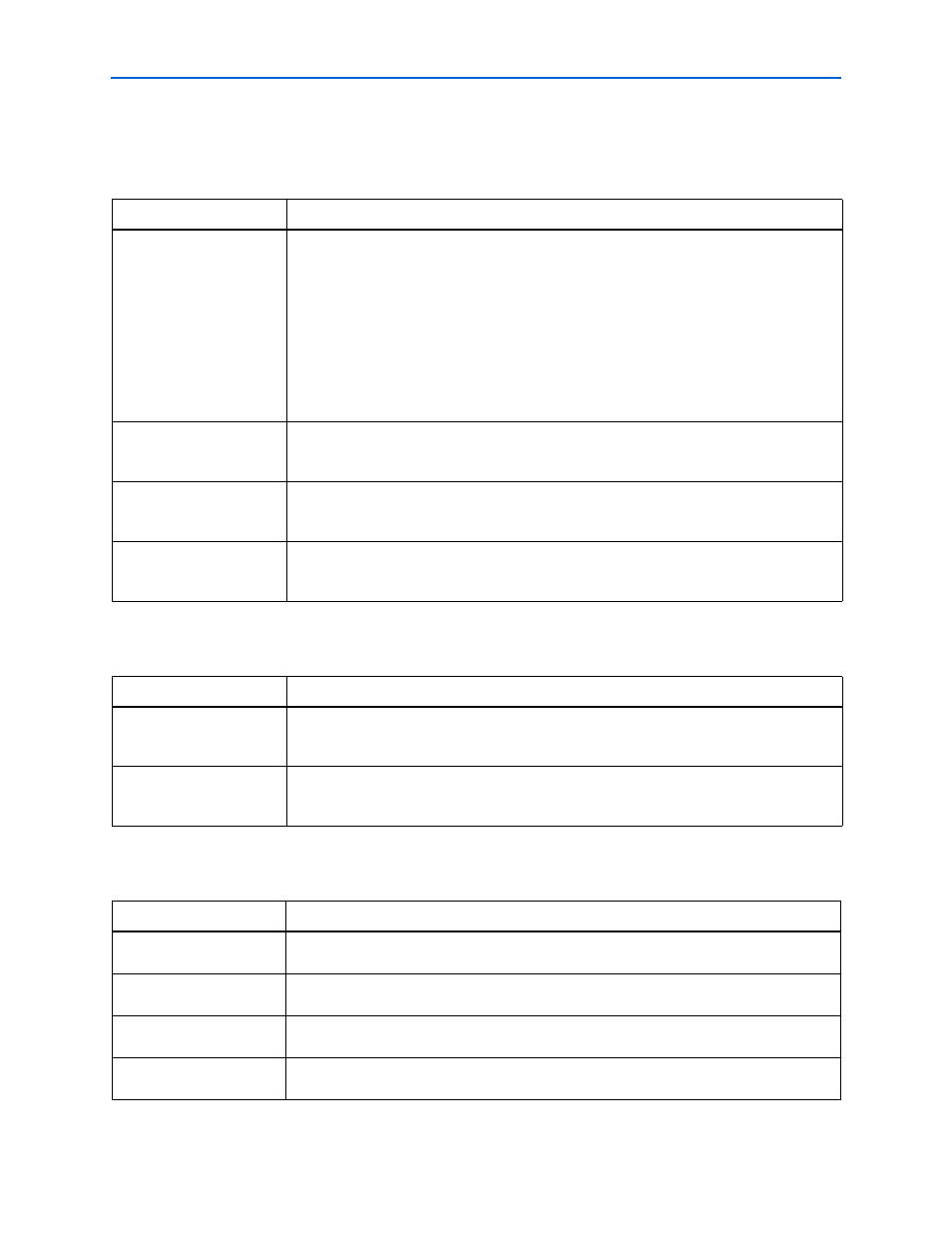

Table 3–22. Example Design Options

Parameter

Description

Update the example design

file that instantiates the

controller variation

When this option is turned on, IP Toolbench parses and updates the example design file. It

only updates sections that are between the following markers:

<

<

If you edit the example design file, ensure that your changes are outside of the markers or

remove the markers. Once you remove the markers, you must keep the file updated, because

IP Toolbench can no longer update the file.

When you turn on this option, IP Toolbench updates the example testbench and the ModelSim

simulation script.

Automatically apply

datapath-specific contraints

to the Quartus II project

When this option is turned on, the next time you compile, the Quartus II software

automatically runs the add constraints script. Turn off this option if you do not want the script

to run automatically

Automatically verify

datapath-specific timing in

the Quartus II project

When this option is turned on, after every compilation the Quartus II software automatically

runs the verify timing script. Turn off this option if you do not want the script to run

automatically.

Update the example design

PLLs

When this option is turned on, IP Toolbench automatically overwrites the PLLs.Turn off this

option, if you do not want the wizard to overwrite the system PLL or the optional fed-back

PLL.

Table 3–23. Variation Path Options

Parameter

Description

Enable hierarchy control

The constraints script analyzes your design, to automatically extract the hierarchy to your

variation. To prevent the constraints script analyzing your design, turn on Enable hierarchy

control, and enter the correct hierarchy path to your datapath.

Hierarchy path to your

custom variation

The hierarchy path is the path to your DDR or DDR2 SDRAM datapath, minus the top-level

name. The hierarchy entered in the wizard must match your design, because the constraints

and timing scripts rely on this path for correct operation.

Table 3–24. Device Pin Prefixes & Names Options

Parameter

Description

Pin name of the clock

driving the memory (+)

The suggested clk_to_sdram pin name, which you may edit, but must end in [0].

Pin name of the clock

driving the memory (–)

The suggested clk_to_sdram_n pin name, which you may edit, but must end in [0].

Pin name of fed-back clock

input

The suggested fedback_clock_in pin name, which you may edit.

Pin prefix all pins on the

devices with

This string is used to prefix the pin names for the FPGA pins connected to the DDR or DDR2

SDRAM.