Performance and resource utilization, Performance and resource utilization –4 – Altera DDR SDRAM Controller User Manual

Page 8

1–4

Chapter 1: About This Compiler

Performance and Resource Utilization

DDR and DDR2 SDRAM Controller Compiler User Guide

March 2009

Altera Corporation

■

Burst lengths:

■

2, 4, or 8, for DDR SDRAM

■

4, for DDR2 SDRAM

■

Banks:

■

4 for DDR SDRAM

■

4 or 8 for DDR2 SDRAM

■

Support for ODT in DDR2 SDRAM

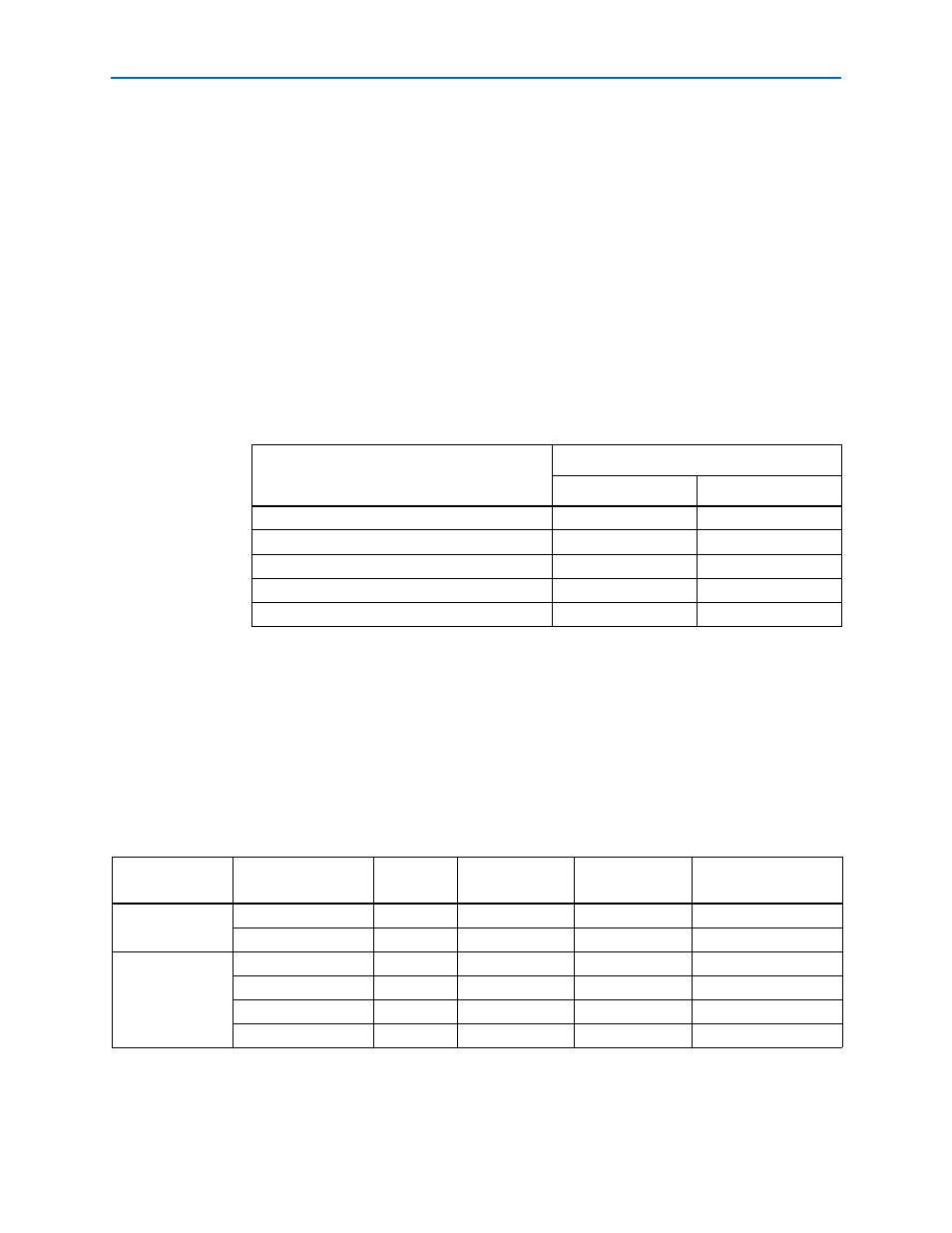

Performance and Resource Utilization

shows typical performance results for the DDR SDRAM controller using the

Quartus II software version 9.0.

f

For more information on device performance, refer to the relevant device handbook.

shows typical sizes in logic elements (LEs) or adaptive look-up tables

(ALUTs) for the DDR SDRAM controller.

Table 1–3. Typical Performance

Device

System fMAX (MHz)

DDR SDRAM

DDR2 SDRAM

Cyclone (EP1C20F400C6)

133

–

Cyclone II (EP2C35F672C6)

167

167

Stratix (EP1S25F780C5)

200

–

Stratix II (EP2S60F1020C3)

200

Stratix II GX (EP2SGX30CF780C3)

267

Note to

:

(1) For information on a solution that achieves speeds greater than 267 MHz (533 Mbps) up to 333 MHz (667 Mbps),

contact your local Altera sales representative. To achieve speeds greater than 267 MHz, a new dynamic

autocalibration circuit is required.

(2) Pending device characterization.

Table 1–4. Typical Size (Part 1 of 2)

Device

Memory Width (Bits)

LEs

Combinational

ALUTs

Logic Registers

M4K RAM Blocks

Cyclone

16

860

—

—

1

32

1,050

—

—

2

Cyclone II

16

940

—

—

1

32

1,120

—

—

2

64

1,500

—

—

4

72

1,600

—

—

5