Simulate the example design, Simulate the example design –17, Note 1) – Altera DDR SDRAM Controller User Manual

Page 27

Chapter 2: Getting Started

2–17

MegaWizard Plug-In Manager Design Flow

© March 2009

Altera Corporation

DDR and DDR2 SDRAM Controller Compiler User Guide

2. After you review the generation report, click Exit to close IP Toolbench.

1

The Quartus II IP File (.qip) is a file generated by the MegaWizard interface or SOPC

Builder that contains information about a generated IP core. You are prompted to add

this .qip file to the current Quartus II project at the time of file generation. In most

cases, the .qip file contains all of the necessary assignments and information required

to process the core or system in the Quartus II compiler. Generally, a single .qip file is

generated for each MegaCore function and for each SOPC Builder system. However,

some more complex SOPC Builder components generate a separate .qip file, so the

system .qip file references the component .qip file.

You have finished the walkthrough. Now, simulate the example design (see

“Simulate the Example Design” on page 2–17

), edit the PLL(s), and compile (refer to

“Compile the Example Design” on page 2–22

).

Simulate the Example Design

You can simulate the example design with the IP Toolbench-generated IP functional

simulation models. IP Toolbench generates a VHDL or Verilog HDL testbench for

your example design, which is in the testbench directory in your project directory.

f

For more information on the testbench, refer to

You can use the IP functional simulation model with any Altera-supported VHDL or

Verilog HDL simulator. The instructions for the ModelSim simulator are different to

other simulators.

Simulating With the ModelSim Simulator

To simulate the example design with the ModelSim

®

simulator, follow these steps:

1. Obtain a memory model that matches your chosen parameters and save it to the

<directory name>\testbench directory. For example, you can download a Micron

memory model from the Micron web site

.

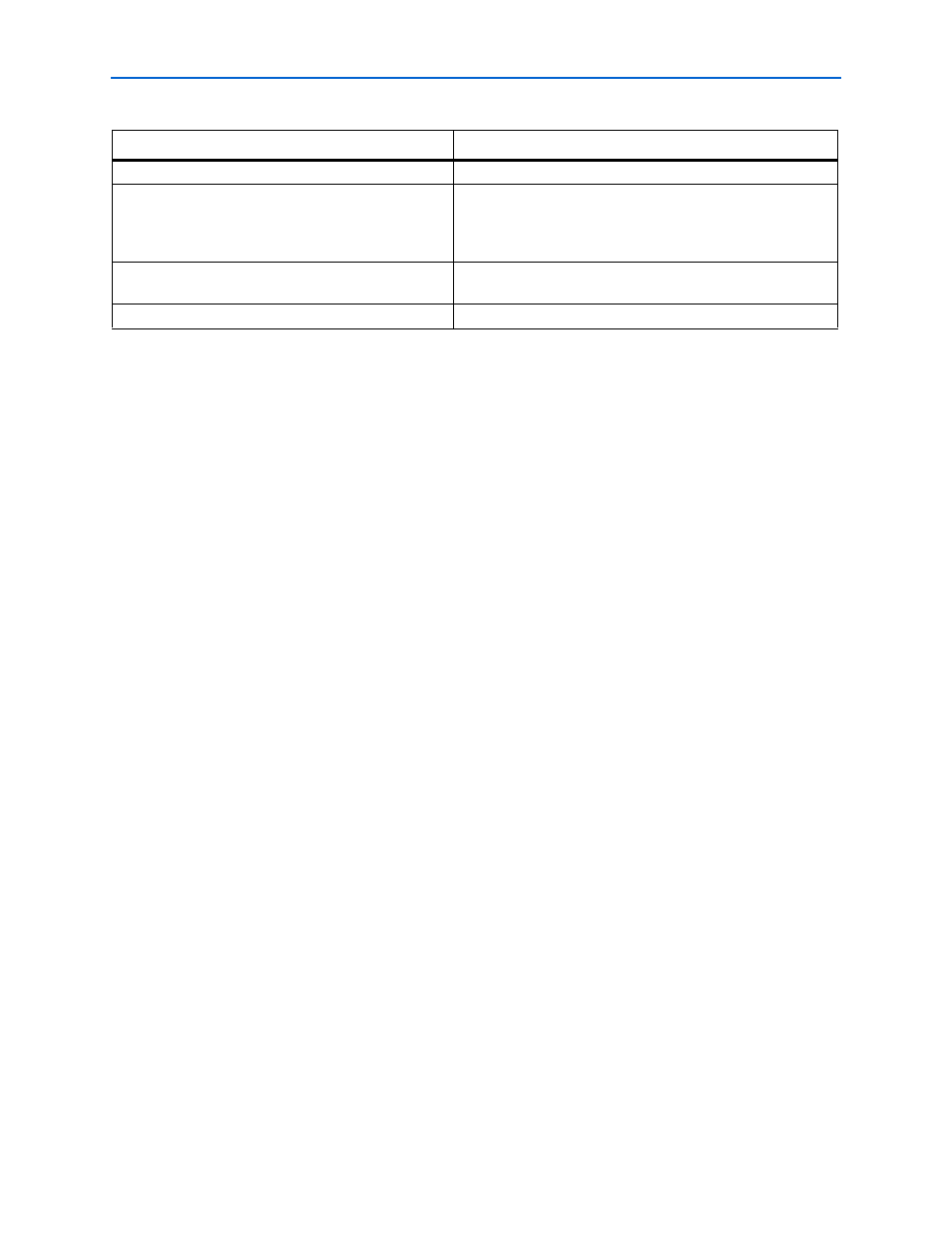

remove_constraints_for_

The remove constraints script for the variation.

top_ddr_settings.txt

Critical settings file that stores the custom variation’s

parameters. IP Toolbench uses this file to generate the add

constraints script. The verify timing script and the DDR Timing

Wizard also read this file.

top_pre_compile_ddr_timing_summary.txt

Log file that stores the results of the precompilation system

timing analysis.

verify_timing_for_

The verify timing script.

Notes to

(1)

(2)

Table 2–1. Generated Files (Part 2 of 2)

(Note 1)

(2)

Filename

Description