Altera DDR SDRAM Controller User Manual

Page 31

Chapter 2: Getting Started

2–21

MegaWizard Plug-In Manager Design Flow

© March 2009

Altera Corporation

DDR and DDR2 SDRAM Controller Compiler User Guide

Verilog HDL IP Functional Simulations

For Verilog HDL simulations with IP functional simulation models, follow these

steps:

1. Create a directory in the <project directory>\testbench directory.

2. Launch your simulation tool inside this directory and create the following

libraries.:

■

altera_mf_ver

■

lpm_ver

■

sgate_ver

■

<device name>_ver

■

auk_ddr_user_lib

3. Compile the files in

into the appropriate library.

4. Set the Tcl variable gRTL_DELAYS to 1, which tells the testbench to model the

extra delays in the system necessary for RTL simulation.

5. Configure your simulator to use transport delays, a timestep of picoseconds and to

include the sgate_ver, lpm_ver, altera_mf_ver, and <device name>_ver libraries.

Verilog HDL Gate-Level Simulations

For Verilog HDL simulations with gate-level models, follow these steps:

1. Create a directory in the <project directory>\testbench directory.

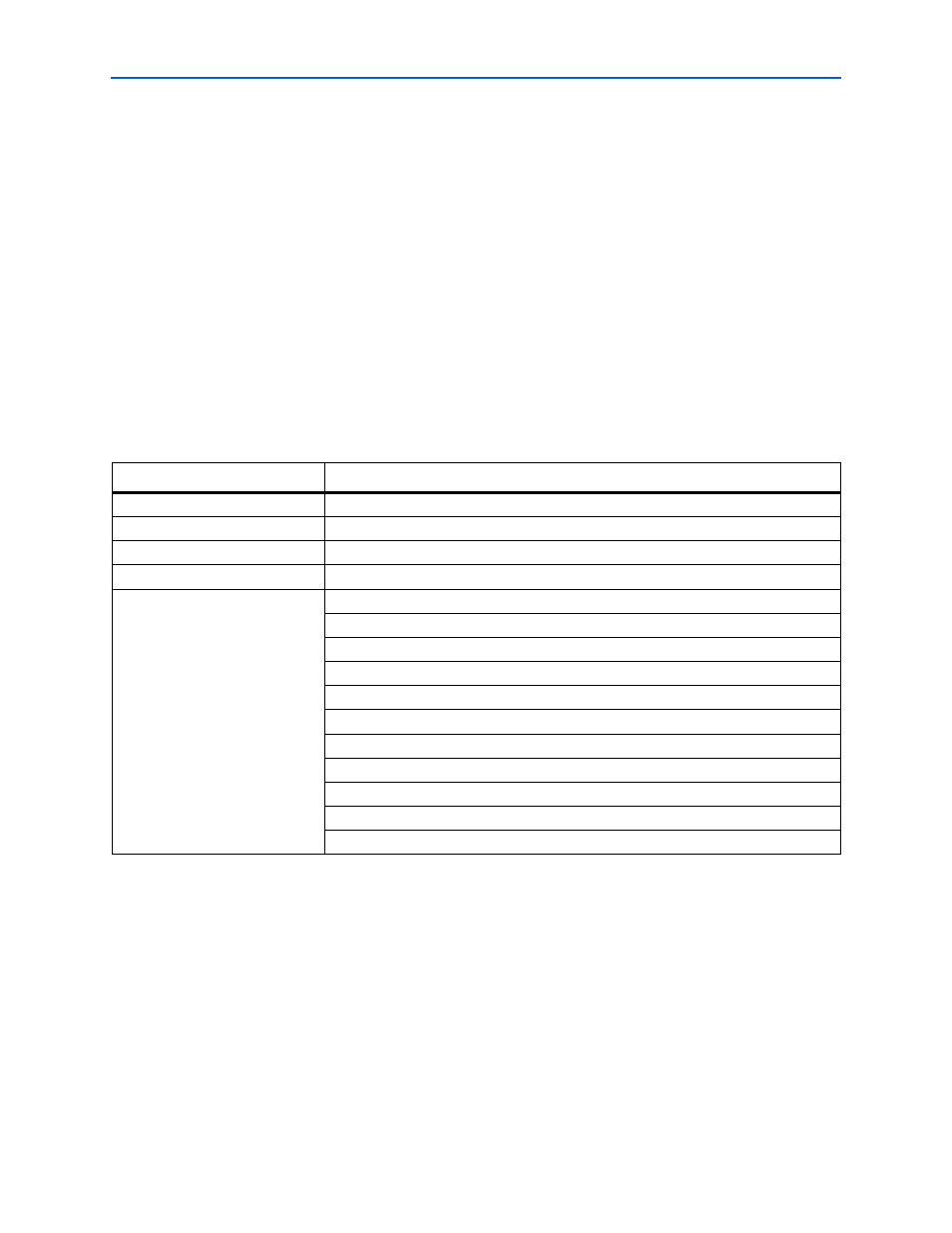

Table 2–4. Files to Compile—Verilog HDL IP Functional Simulation Models

Library

Filename

altera_mf_ver

<QUARTUS ROOTDIR>/eda/sim_lib/altera_mf.v

lpm_ver

<QUARTUS ROOTDIR>/eda/sim_lib/220model.v

sgate_ver

<QUARTUS ROOTDIR>/eda/sim_lib/sgate.v

<device name>_ver

<QUARTUS ROOTDIR>/eda/sim_lib/<device name>_atoms.v

auk_ddr_user_lib

<project directory>/<variation name>_auk_ddr_dqs_group.v

<project directory>/<variation name>_auk_ddr_clk_gen.v

<project directory>/<variation name>_auk_ddr_datapath.v

<project directory>/<variation name>.vo

<MegaCore install directory>/lib/example_lfsr8.v

<project directory>/<variation name>_example_driver.v

<project directory>/ddr_pll_<device name>.v

<project directory>/ddr_pll_fb_<device name>.v

<project directory>/<variation name>_auk_ddr_dll.v

<project directory>/<project name>.v

<project directory>/testbench/<testbench name>.v

Notes to

(1) Fed-back clock mode only.

(2) Stratix series only.