Resynchronization, R to, Resynchronization” on – Altera DDR SDRAM Controller User Manual

Page 82

A–4

Resynchronization

DDR and DDR2 SDRAM Controller Compiler User Guide

© March 2009

Altera Corporation

shows the timing analysis options.

Resynchronization

Resynchronization is the process of transferring data from the read DQS clock domain

back to the system clock domain. The phase relationship of DQS to the system clock

can be calculated for your specific hardware setup and depends on the round trip

delay. The round trip delay is the time it takes for the read command to reach the

memory and for the read data to return to and be captured into the Altera device.

The DDR and DDR2 SDRAM Controller Compiler provides a variety of

resynchronization clocking schemes. The wizard automatically chooses the best

scheme for your system based on the parameters that you enter. The data is

transferred from the read DQS clock domain to a resynchronization clock domain

before final transfer to the system clock domain. The resynchronization clock can be

the positive or negative edge of either the system clock or the write clock. If safe

resynchronization cannot be guaranteed using one of these four phases, a separate

output of the phase-locked loop (PLL) is used as the resynchronization clock. If the

resynchronization clock phase is close to the positive edge of the system clock, an

additional set of registers, clocked on the negative edge of system clock, is inserted

between the resynchronization clock domain and the system clock domain.

You can choose to have the read data at the output of the DDR or DDR2 SDRAM

controller (local_rdata) reclocked to the positive edge of the system clock domain

by turning on Reclock resynchronized data to the positive edge on the Manual

Timing

tab of the wizard. If you do not turn it on, the output data is clocked by the

resynchronization clock and it is your responsibility to transfer it to the system clock

domain.

If you wish to specify your own resynchronization clock instead of using the

automatically selected one, you can do so on the Manual Timing tab of the wizard. If

you require more control than is available on the Manual Timing tab, you can modify

the example design created by the wizard to connect the resynchronization clock to

any clock source.

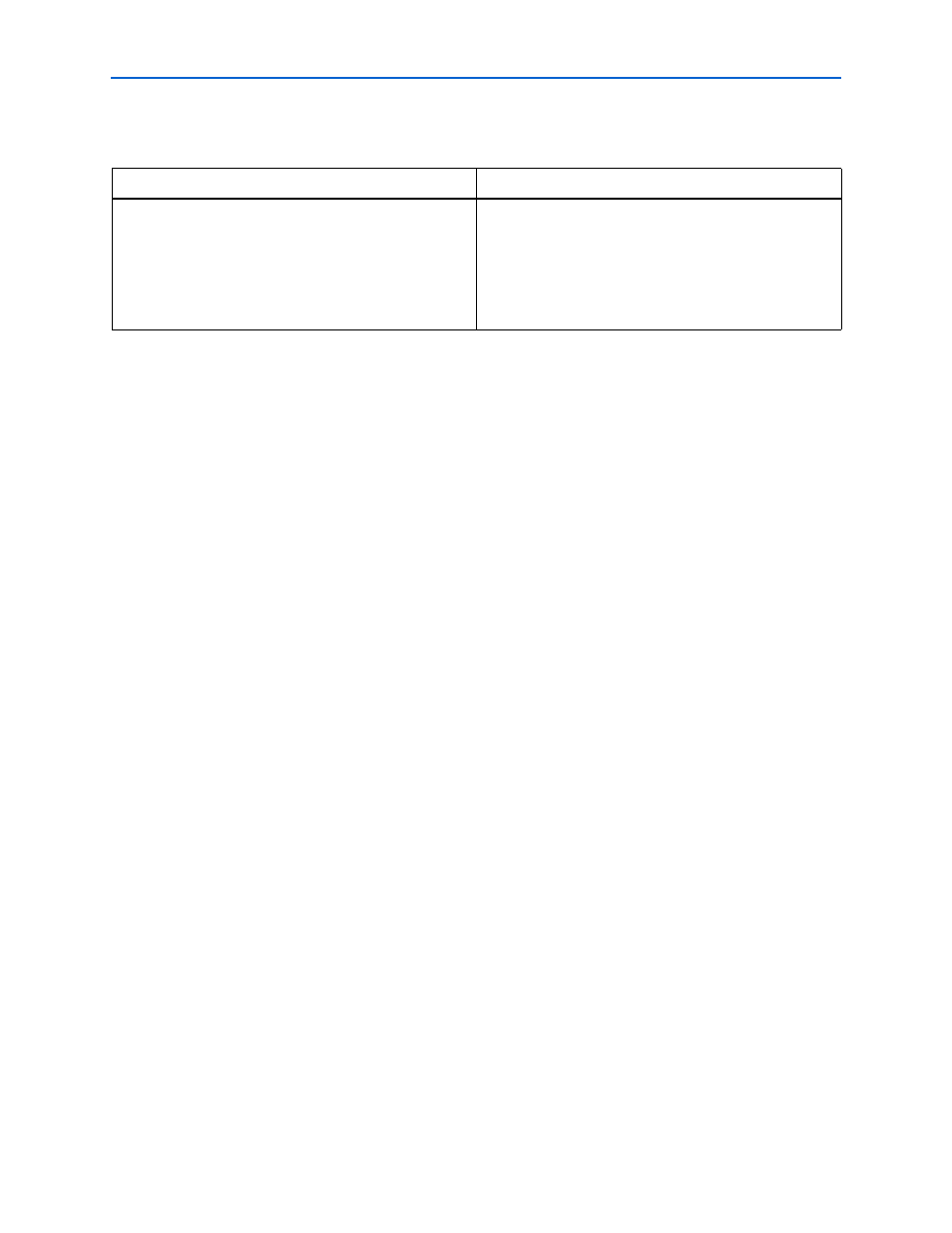

Table A–4. Timing Analysis Options

Parameter

Description

Use the results of the last compile to estimate the setup and

hold margins

Turn on to achieve a better estimate of the setup and hold

margins your design is likely to achieve. It also allows the

wizard to pick more accurate phases for the

resynchronization, postamble, and capture clocks. You must

successfully compile your design and run the verify timing

script to generate the necessary updated estimates file,

before you can use this option.