Resynch_clk, Ster (refer to, Figure 3–19 – Altera DDR SDRAM Controller User Manual

Page 65

Chapter 3: Functional Description

3–29

Interfaces & Signals

© March 2009

Altera Corporation

DDR and DDR2 SDRAM Controller Compiler User Guide

shows the DDR and DDR2 SDRAM controller local interface signals.

write_clk

Input

Shifted clock that center aligns write data to the memory.

dqs_ref_clk

Output

Stratix DLL reference clock output.

fedback_clock_out

Output

Fed-back clock output.

stratix_dll_control

Output

Disables the Stratix DLL reference clock during reads.

Note to

(1) This signal only exists on the custom variation when a dedicated clock phase is required, otherwise the connection is made inside the custom

variation.

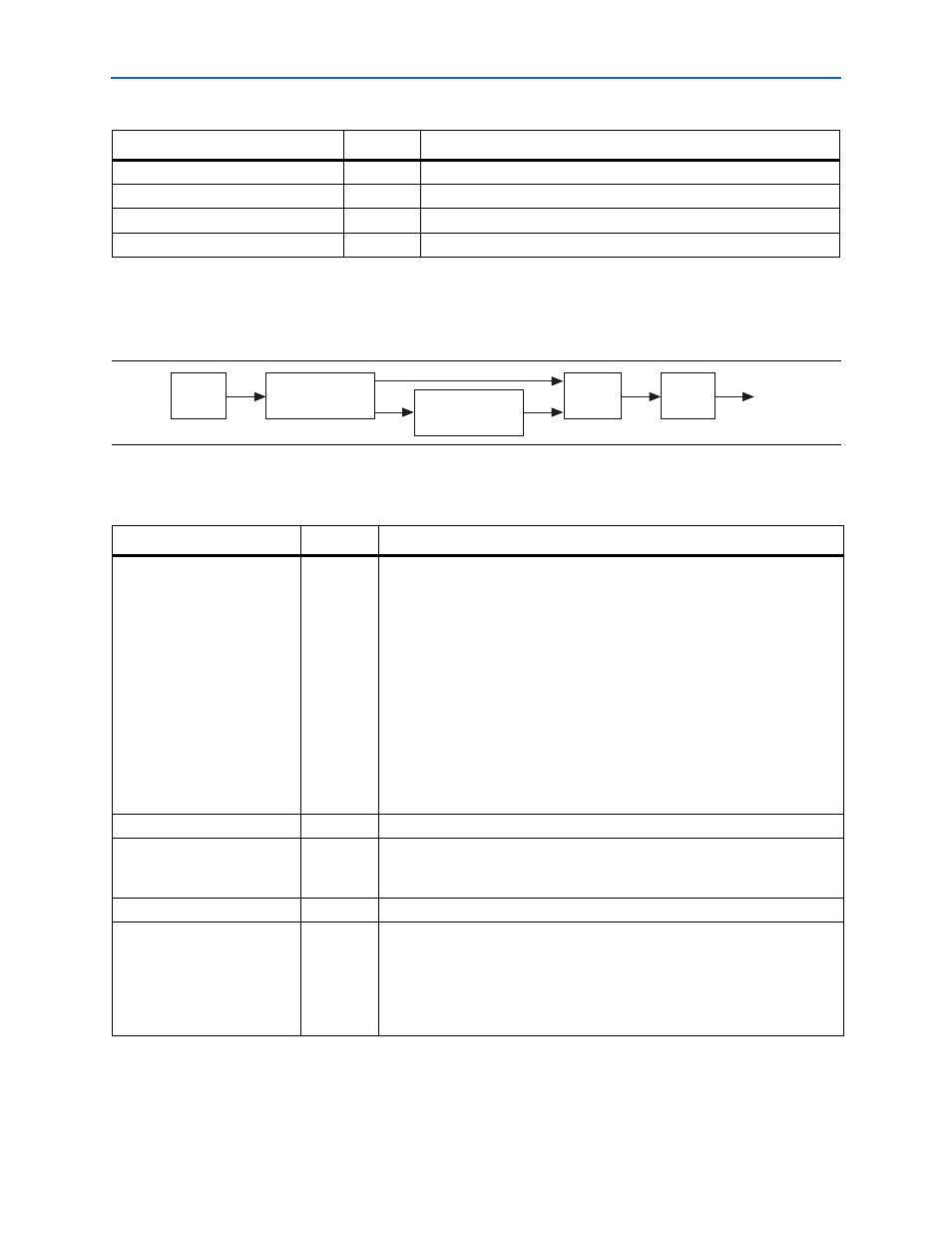

Figure 3–19. Circuit for resynch_clk_edge_select

Table 3–7. System Signals (Part 2 of 2)

Signal Name

Direction

Description

Capture

Register

Multiplex

local_rdata

Pipeline

Register

Extra

Resynchronization

Register

Resynchronization

Register

Table 3–8. Local Interface Signals (Part 1 of 2)

Signal Name

Direction

Description

local_addr[]

Input

Memory address at which the burst should start. The width of this bus is sized

using the following equation:

For one chip select:

width = bank bits + row bits + column bits – 1

For multiple chip selects:

width = chip bits + bank bits + row bits + column bits – 1

The least significant bit (LSB) of the column address on the memory side is

ignored, because the local data width is twice that of the memory data bus

width.

The order of the address bits is set in the clear text part of the MegaCore

function (auk_ddr_sdram.vhd). The order is chips, bank, row, column, but

you can change it if required.

local_be[]

Input

Byte enable signal, which you use to mask off individual bytes during writes.

local_burstbegin

Input

Avalon-MM burst begin strobe, which indicates the beginning of an Avalon-

MM burst. This signal is only available when the local interface is an Avalon-

MM interface and the memory burst length is greater than 2.

local_read_req

Input

Read request signal.

local_refresh_req

Input

User controlled refresh request. If User Controlled Refresh is turned on,

local_refresh_req

becomes available and you are responsible for

issuing sufficient refresh requests to meet the memory requirements. This

option allows complete control over when refreshes are issued to the memory

including ganging together multiple refresh commands. Refresh requests take

priority over read and write requests unless they are already being processed.