Altera DDR SDRAM Controller User Manual

Page 7

Chapter 1: About This Compiler

1–3

General Description

March 2009

Altera Corporation

DDR and DDR2 SDRAM Controller Compiler User Guide

The DDR SDRAM Controller is optimized for Altera Stratix and Cyclone series; the

DDR2 SDRAM Controller is optimized for Altera Stratix II and Cyclone II devices

only. The advanced features available in these devices allow you to interface directly

to DDR or DDR2 SDRAM devices and to use the DQS signal in the read and write

direction.

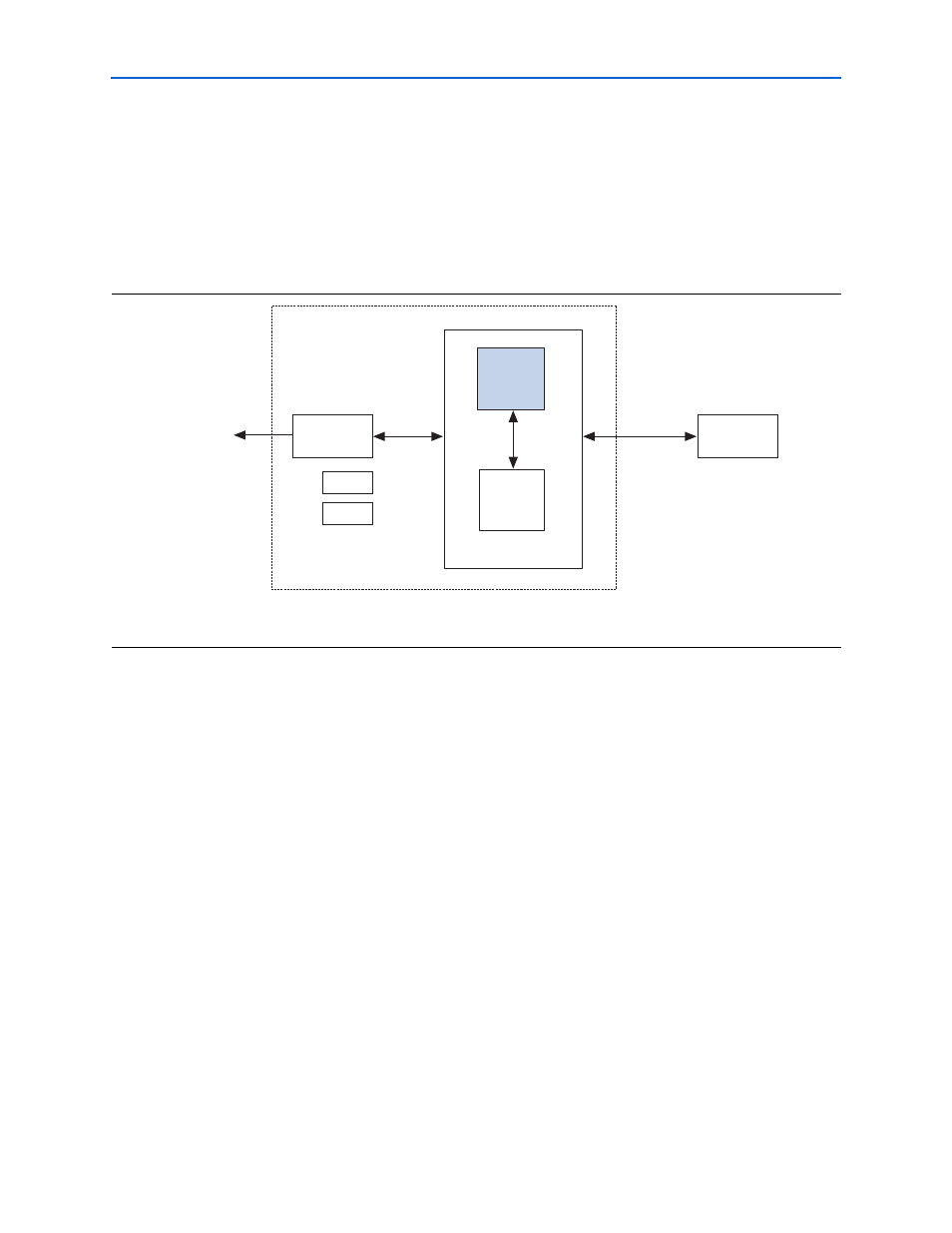

shows a system-level diagram including the example design that the DDR

or DDR2 SDRAM Controller MegaCore functions create for you.

Whether you use IP Toolbench in SOPC Builder or in the Quartus II software, it

generates example design, instantiates a phase-locked loop (PLL), an example driver,

your DDR or DDR2 SDRAM controller custom variation, and an optional DLL (for

Stratix series only). The example design is a fully-functional design that can be

simulated, synthesized, and used in hardware. The example driver is a self-test

module that issues read and write commands to the controller and checks the read

data to produce the pass/fail and test complete signals.

You can replace the DDR or DDR2 SDRAM controller encrypted control logic in the

example design with your own custom logic, which allows you to use the Altera

clear-text datapath with your own control logic.

The DDR and DDR2 SDRAM Controllers are very similar. The following differences

exist:

■

Initialization timing (refer to

“DDR SDRAM Initialization Timing” on page 3–25

“DDR2 SDRAM Initialization Timing” on page 3–26

)

■

CAS latency options:

■

2.0, 2.5, or 3.0, for DDR SDRAM

■

3, 4, or 5, for DDR2 SDRAM

Figure 1–1. DDR & DDR2 SDRAM Controller System-Level Diagram

Note to

(1) Optional, for Stratix series and HardCopy II devices only.

DDR SDRAM

Example Driver

PLL

DLL (

1

)

DDR SDRAM

Interface

Pass or Fail

Local

Interface

Example Design

Control

Logic

(Encrypted)

DDR SDRAM Controller

Data Path

(Clear Text)