Altera DDR SDRAM Controller User Manual

Page 41

Chapter 3: Functional Description

3–5

Device-Level Description

© March 2009

Altera Corporation

DDR and DDR2 SDRAM Controller Compiler User Guide

In the write direction, the wdata_valid signal acts as an enable on the

local_wdata

registers. The output of these registers is clocked into registers in the

IOE where it is fed to the DQ pins. The registers in the IOE are clocked by the write

clock (which is 90° before the system clock) so that DQS, which is generated by the

datapath, appears in the center of the data on the DQ pins. The write DQS is

generated from registers clocked by the system clock so that the t

DQSS

parameter is met

at the DDR or DDR2 SDRAM device.

shows the interface to the datapath.

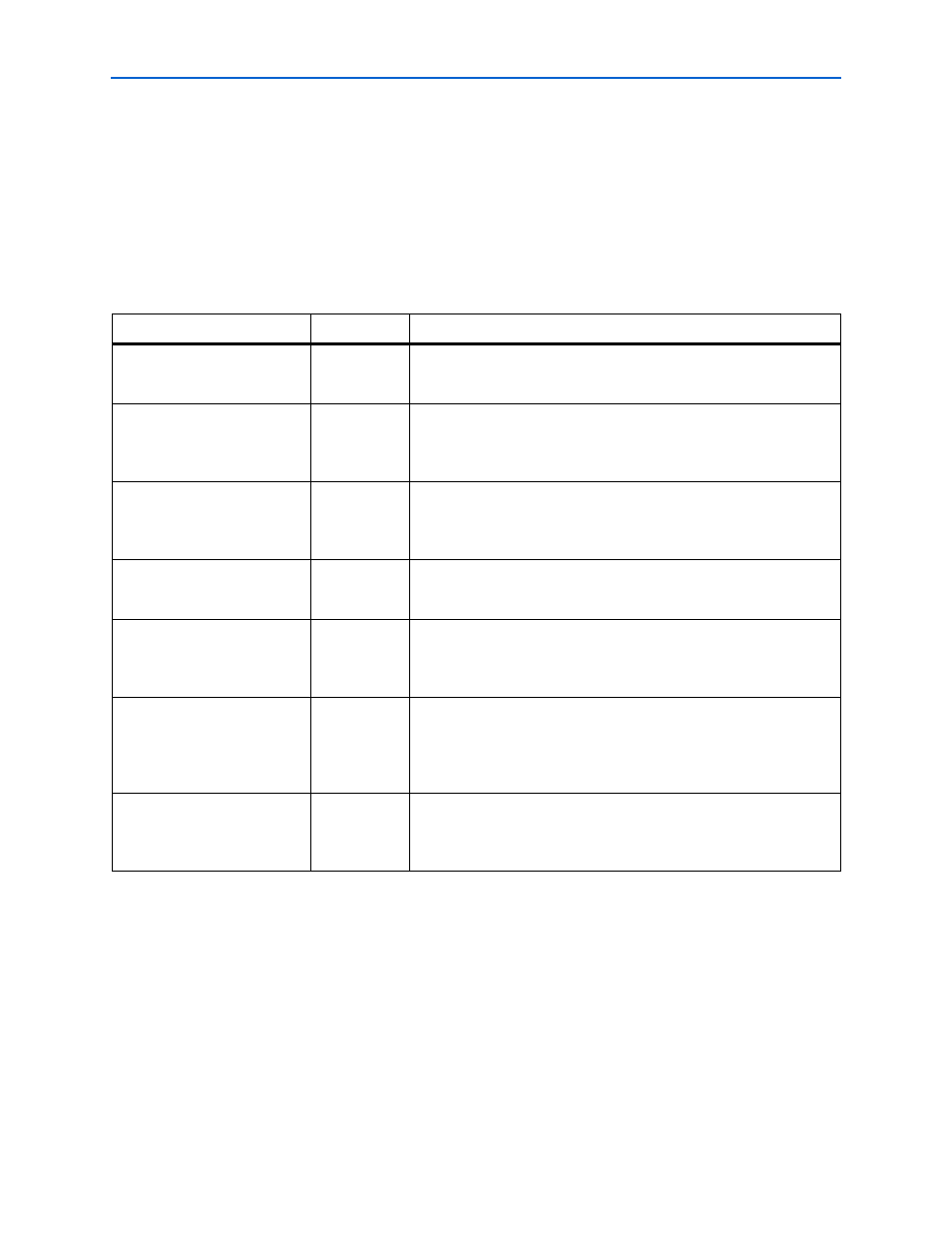

Table 3–3. Datapath Interface

Signal name

Direction

Description

control_doing_wr

Input

The control_doing_wr signal is asserted when the controller is

writing to the DDR or DDR2 SDRAM and controls the output enables on

the DQ pins.

control_wdata_valid

Input

The control_wdata_valid signal is a registered version of the

write data request to the local interface. It enables the write data and

byte enable registers so that they are only updated when valid data and

enables are available.

control_dqs_burst

Input

The control_dqs_burst signal controls the output enables of the

DQS pins. The DQS output enable must be asserted for longer than the

DQ output enable, particularly when the local burst size is shorter than

the memory burst length.

control_wdata[]

Input

The control_wdata signal is the write data bus and should have

valid data in the same clock cycle that control_wdata_valid is

asserted.

control_be[]

Input

The control_be signal is the byte enable bus and should have valid

data in the same clock cycle that control_wdata_valid is

asserted. The byte enables are converted into DDR or DDR2 SDRAM

data mask signals.

control_doing_rd

Input

The control_doing_rd signal is asserted when the controller is

reading from the DDR or DDR2 SDRAM and enables the DQ capture

registers. It also controls the postamble control registers to prevent the

DQ capture registers from being inadvertently clocked after the DQS

read postamble.

control_rdata[]

Output

The control_rdata bus is the read data bus and has valid data

some clock cycles after the read command is issued. The exact

relationship depends on the CAS latency of the memory and whether or

not registered DIMMs are being used.