Constraints, Constraints –18 – Altera DDR SDRAM Controller User Manual

Page 54

3–18

Chapter 3: Functional Description

Device-Level Description

DDR and DDR2 SDRAM Controller Compiler User Guide

© March 2009

Altera Corporation

The testbench instantiates a DDR or DDR2 SDRAM DIMM model, a reference clock

for the PLL, and model for the system board memory trace delays. When

test_complete

is detected high, a test finished message is printed out, which

shows whether the test has passed.

1

Altera does not provide a memory simulation model. You must obtain one from your

memory vendor.

f

For more details on how to run the simulation script, refer to

.

Constraints

IP Toolbench generates a constraints script, add_constraints_for_

which is a set of Quartus II assignments that are required to successfully compile the

example design.

1

When the constraints script runs, it creates another script,

remove_constraints_for_

constraints from your design.

The constraints script implements the following types of assignments:

■

Capacitance loading for SDRAM interface pins

■

I/O standard to SSTL-2 class II for DDR SDRAM interface pins (SSTL-18 class II

for DDR2 SDRAM)

■

Current strength set to “min” for Stratix devices

■

DM, DQ, and DQS pin placement (except for non-DQS mode on Stratix devices)

■

Resynchronization and postamble registers placement

■

I/O register placement for Cyclone series

■

Synthesis “Don’t Optimize” set for the datapath logic

■

Address and control fast output register constraints

■

DQS frequency and delay settings for Cyclone devices

1

As the static timing analysis performed after the design compiles requires that the all

the clocks in the datapath are global, you must ensure you do not use regional clocks

for the datapath logic.

shows the methods that achieve the logic placement constraints.

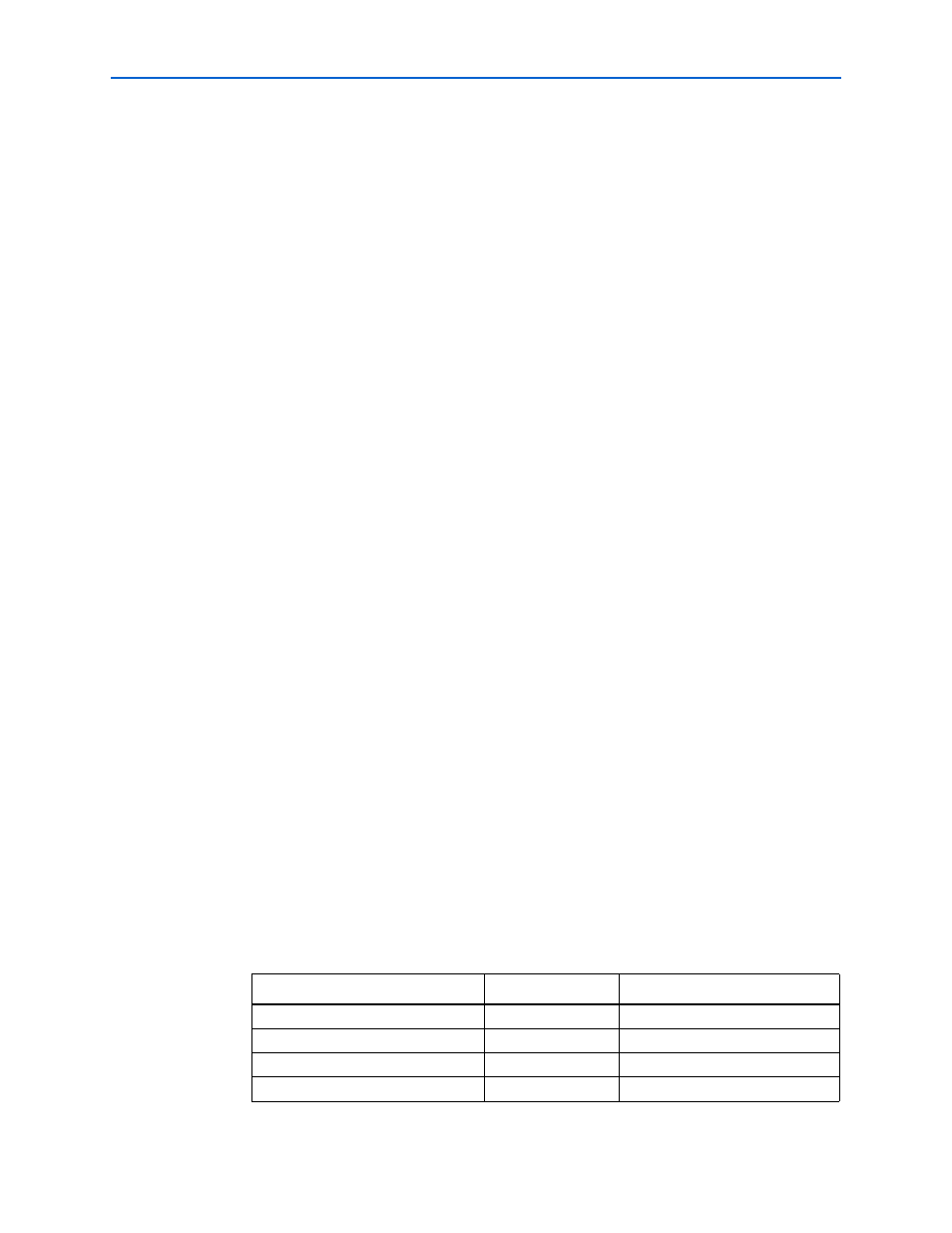

Table 3–6. Methods for Logic Placement Constraints

Device Family

Capture Registers

Resynchronization Registers

Stratix II/Stratix II GX

—

LAB placement

Stratix/Stratix GX

—

LogicLock region constraints

Cyclone II

LAB placement

LAB placement

Cyclone

LE placement

LE placement