Installation and licensing, Installation and licensing –5, Note 1) – Altera DDR SDRAM Controller User Manual

Page 9

Chapter 1: About This Compiler

1–5

Installation and Licensing

March 2009

Altera Corporation

DDR and DDR2 SDRAM Controller Compiler User Guide

The performance of the entire system and in general the DDR or DDR2 SDRAM

controller depends upon the number of masters and slaves connected to the Avalon

®

Memory-Mapped (Avalon-MM) interface, which degrades as the number of masters

and slaves connected to it increases. If the number of masters connected to the slave

increases, the size of the arbiter (which is part of the Avalon-MM interface) increases,

which reduces the performance of the system. The DDR or DDR2 SDRAM controller

performance is limited by the frequency of Avalon-MM interface.

There is no latency associated within the Avalon-MM interface, when it transfers the

read or write request to the controller local interface. If there are multiple masters

connected to the DDR or DDR2 SDRAM controller, there may be wait states before

the request from the master is accepted by the controller.

f

For more information, refer to the System Interconnect Fabric for Memory-Mapped

Interfaces chapter in the

Quartus II Handbook

.

Installation and Licensing

The DDR and DDR2 SDRAM Controller Compiler is part of the MegaCore IP Library,

which is distributed with the Quartus

®

II software and downloadable from the Altera

webs

.

f

For system requirements and installation instructions, refer to

and Linux Workstations

.

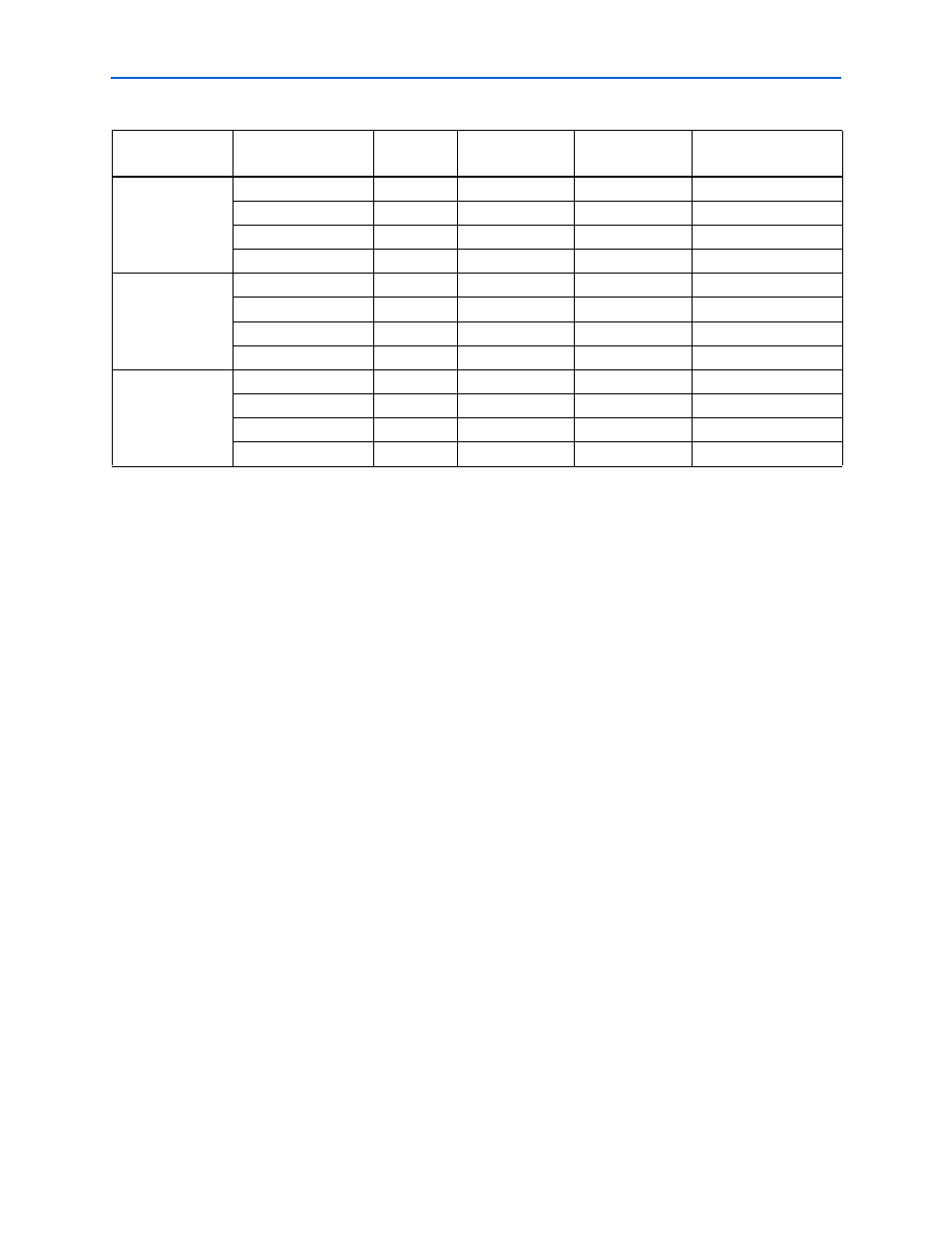

Stratix

16

—

750

—

1

32

—

830

—

2

64

—

1,000

—

4

72

—

1,040

—

5

Stratix II

16

—

800

—

1

32

—

960

—

2

64

—

1,250

—

4

72

—

1,320

—

5

Stratix II GX

16

—

800

—

1

32

—

960

—

2

64

—

1,250

—

4

72

—

1,320

—

5

Notes to

(1) These sizes are a guide only and vary with different choices of parameters. These numbers are created with the default settings for each device

family, varying only the width of the interface. Generally, the controller uses about 700 LEs while the size of the datapath varies with width and

the amount of pipelining and clocking scheme required.

(2) The controller uses M4K RAM blocks to buffer write data from the user logic. If you select a burst length of 1 (2 on the DDR SDRAM side), this

buffer is not necessary and no memory blocks are used in your variation, regardless of data width.

Table 1–4. Typical Size (Part 2 of 2)

(Note 1)

Device

Memory Width (Bits)

LEs

Combinational

ALUTs

Logic Registers

M4K RAM Blocks

(2)