Altera DDR SDRAM Controller User Manual

Page 26

2–16

Chapter 2: Getting Started

MegaWizard Plug-In Manager Design Flow

DDR and DDR2 SDRAM Controller Compiler User Guide

© March 2009

Altera Corporation

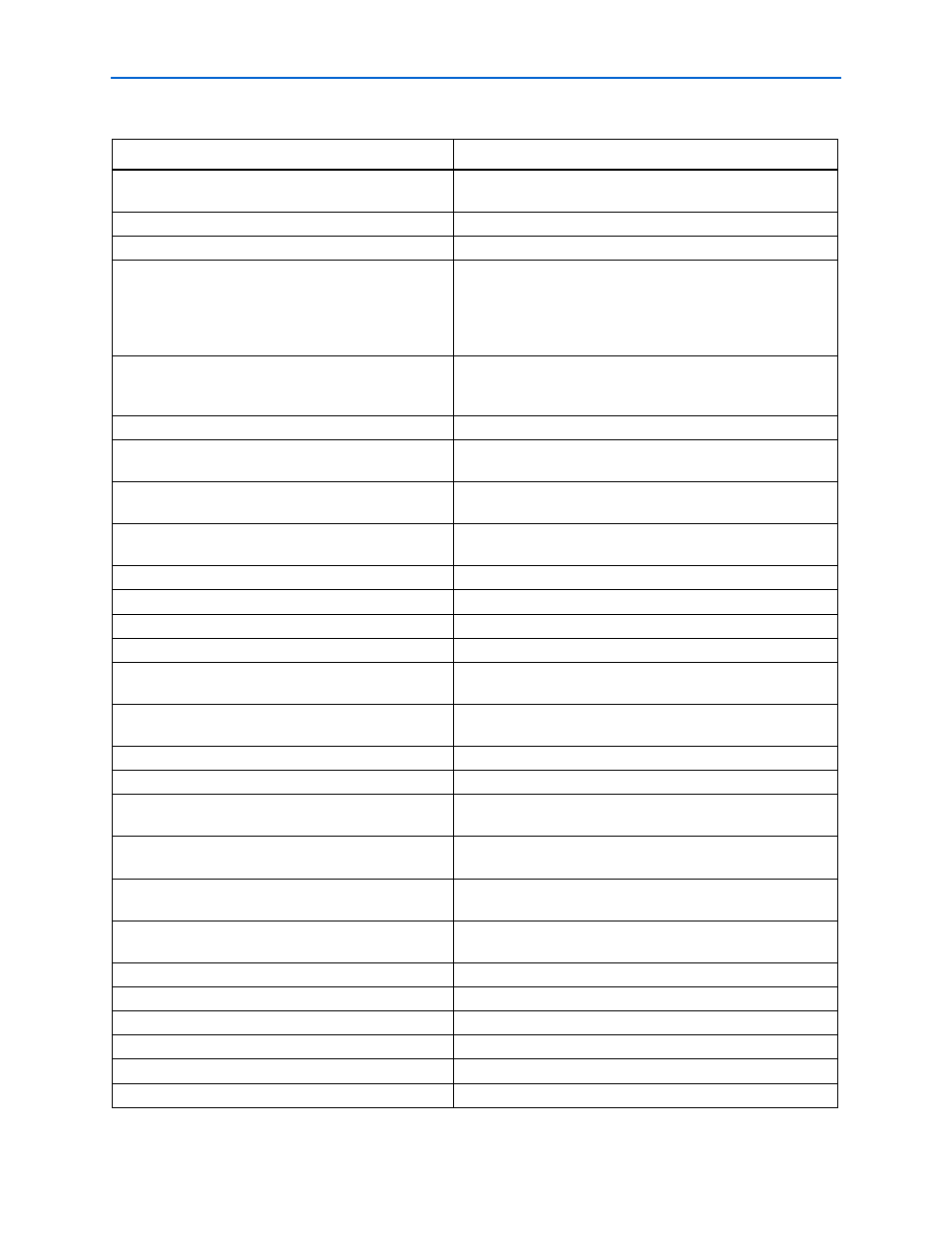

Table 2–1. Generated Files (Part 1 of 2)

Filename

Description

Quartus II symbol file for the MegaCore function variation. You

can use this file in the Quartus II block diagram editor.

MegaCore function report file.

VHDL or Verilog HDL IP functional simulation model.

A MegaCore function variation file, which defines a VHDL or

Verilog HDL top-level description of the custom MegaCore

function. Instantiate the entity defined by this file inside of your

design. Include this file when compiling your design in the

Quartus II software.

Verilog HDL black-box file for the MegaCore function variation.

Use this file when using a third-party EDA tool to synthesize

your design.

Design file that contains the clock output generators.

Design file that instantiates the byte groups and the clock output

generators.

A VHDL package, which contains a component that the IP

functional simulation model uses.

Optional design file that instantiates the Stratix or Stratix II DLL

(Stratix series only).

Design file that contains the datapath byte groups.

Design file that instantiates the controller logic and the datapath

The ModelSim simulation script.

The example driver.

The settings file for your variation, which the add constraints

and the verify timing scripts use.

Contains Quartus II project information for your MegaCore

function variations.

Example design file.

add_constraints_for_

The add constraints script for the variation.

altera_vhdl_support.vhd

A VHDL package that contains functions for the generated

entities. This file may be shared between MegaCore functions.

auto_add_ddr_constraints.tcl

The add constraints script, which calls the variation-specific add

constraints scripts.

auto_verify_ddr_timing_constraints.tcl

The auto verify timing script, which calls the variation-specific

verify timing scripts.

constraints_out.txt

Log file that IP Toolbench creates while generating the add

constraints script.

ddr_lib_path.tcl

The Tcl library path file.

ddr_pll_fb_stratixii.v or .vhd

Design file for the Stratix II fedback PLL.

ddr_pll_

Design file for the system PLL.

generic_ddr_dimm_model.vhd

VHDL simulation file.

generic_ddr_sdram.vhd

VHDL simulation file.

generic_ddr2_sdram.vhd

VHDL simulation file.