Altera DDR SDRAM Controller User Manual

Page 70

3–34

Chapter 3: Functional Description

Parameters

DDR and DDR2 SDRAM Controller Compiler User Guide

© March 2009

Altera Corporation

shows the memory initialization options.

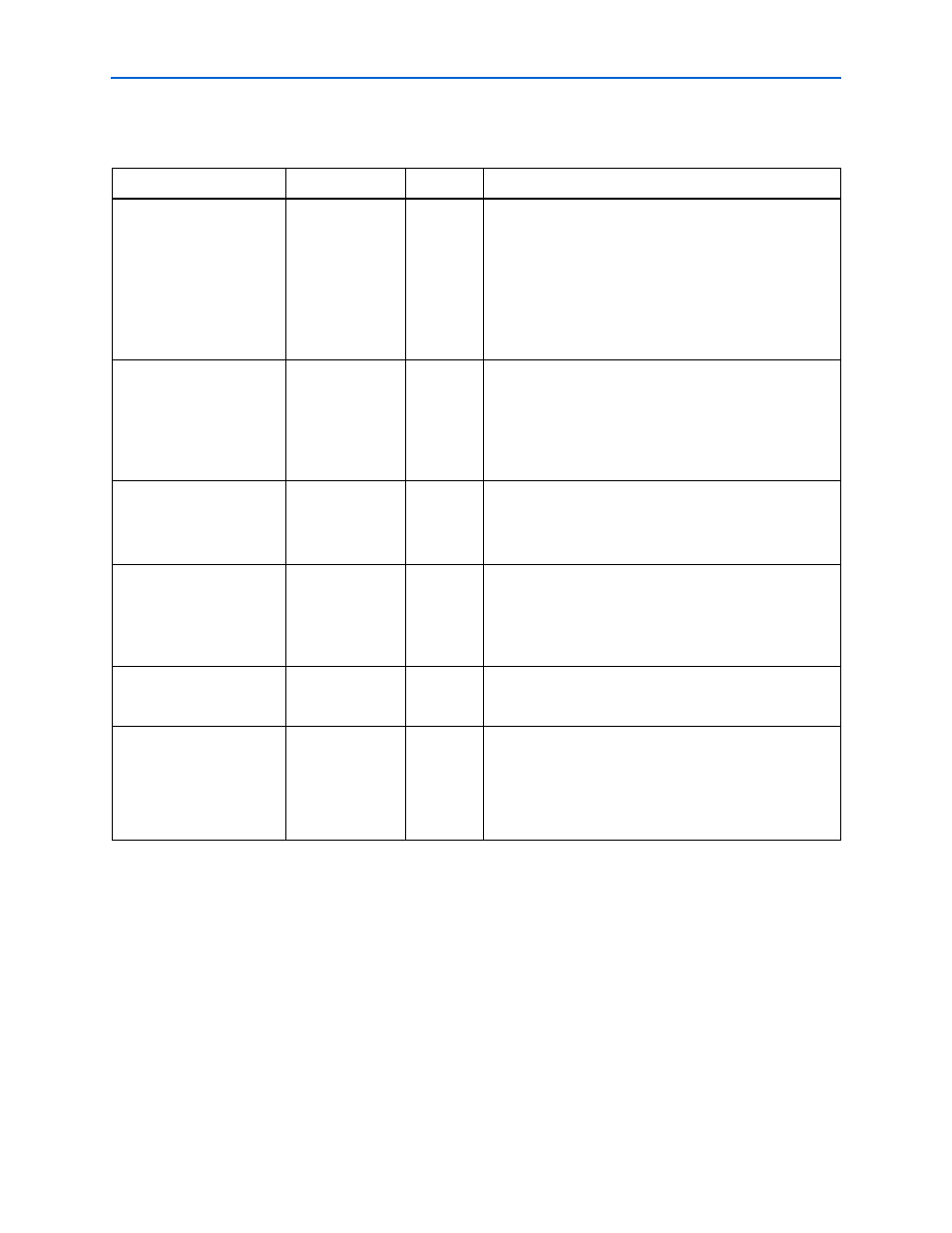

Table 3–14. Memory Initialization Options

Parameter

Range

Units

Description

ODT setting

Disabled, 50, 75,

or 150

Ω

Enables on-die termination (ODT) resistance in the DDR2

SDRAM and enables dynamic control of it by the controller.

Choosing Disabled disable the on-die termination

resistance in the DDR2 SDRAM. The ddr2_odt control

signals are driven with a fixed value of zero.

Choosing 50, 75, or 150

Ω enables a 50-, 75-, or 150-Ω

ODT in the DDR2 SDRAM. The ddr2_odt signals enable

and disable the ODT as required.

CAS latency

2.0, 2.5, or 3.0

(for DDR

SDRAM);

3, 4, or 5

(for DDR2

SDRAM)

Cycles

The delay in clock cycles from the read command to the

first output data from the memory.

Burst length

2, 4, or 8 (for

DDR SDRAM);

4 (for DDR2

SDRAM)

—

The number of data transfers between the FPGA and the

memory in each read or write transaction. The number of

transactions on the local interface is half this value.

Burst type

Sequential or

Interleaved

—

This parameter is a memory Initialization option. Refer to

the memory vendor data sheet for the type of read and

writes transactions that it supports.

Controls the order in which data is transferred between

FPGA and memory during a read or write transaction.

Drive strength

Normal or

Reduced

—

Controls the drive strength of the memory device’s output

buffers. Reduced drive strength is not supported on all

memory devices.

Memory device DLL enable

On or off

—

When turned on, the DLL within the memory device is

enabled. This parameter is a memory Initialization option

and by default turn on this option. Memory vendors do

provide the option of not using the DLL within the memory,

but it is too difficult to perform memory transactions

without the DLL.