A. manual timing settings, Parameters, Appendix a. manual timing settings – Altera DDR SDRAM Controller User Manual

Page 79: Manual, Appendix a, Manual timing settings, Appendix a, manual timing settings, Fer to, Efer to, R to

© March 2009

Altera Corporation

DDR and DDR2 SDRAM Controller Compiler User Guide

A. Manual Timing Settings

Parameters

shows the resynchronization options.

For more information on the resynchronization options, refer to

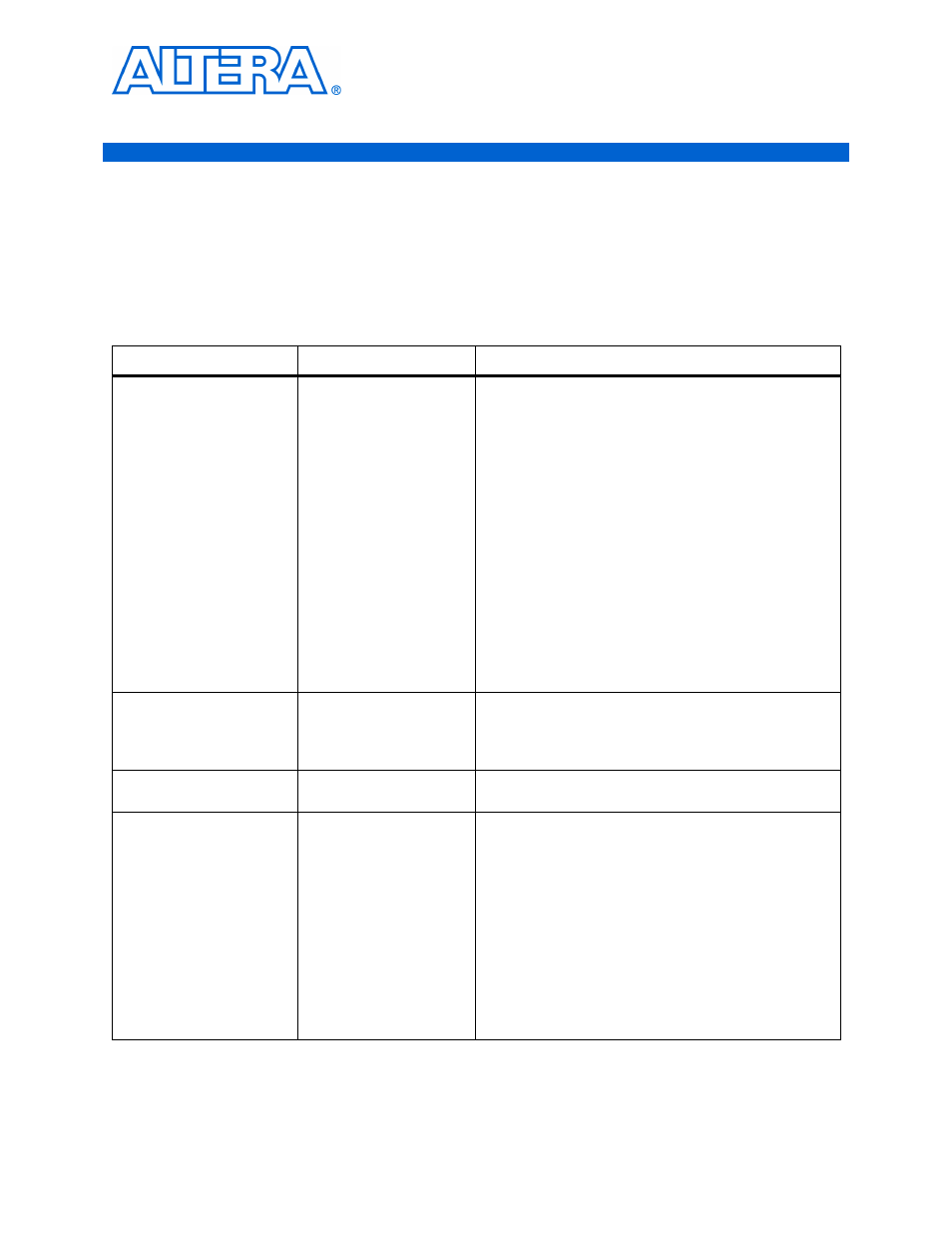

Table A–1. Resynchronization Options (Part 1 of 2)

Parameter

Range

Description

Reclock resynchronized data

to the positive edge

Automatic, Always, or Never When this option is set to “Always” the wizard inserts a set

of positive edge system clock registers in the read data path

and delays the read data valid signal appropriately. The extra

registers are useful if you are resynchronizing with a phase

other than the positive edge of the system clock, but at the

expense of a clock cycle of latency. Choosing Never

produces lower latency. However, it is then your

responsibility to reclock the read data to the positive edge of

the system clock. When this option is set to Automatic, the

wizard decides whether or not to insert the extra set of

registers based on the choice of resynchronization edge and

system clock.

When the resynchronization clock phase is close to the

positive edge of the system clock, this option inserts an

additional set of registers, clocked on the negative edge of

system clock, between the resynchronization clock domain

and the system clock domain.

Manual resynchronization

control

On or off

Turn on to specify the details of the resynchronization clock.

Otherwise, the details are calculated automatically based on

system timing. You must turn on this option when you turn

on the DQS mode and the fedback PLL options.

Resynchronize captured read

data in cycle

0 to 6

The number of cycles of delay to allow for the round trip

delay.

Resynchronization clock

setting

0 (clk, rising edge),

90 (write_clk, falling

edge),

180 (clk, falling edge)

270 (write_clk, rising

edge), or

dedicated

Defines which clock to use for resynchronization: the system

clock, the write clock (a 90

° advanced version of the system

clock), or a dedicated resynchronization clock. Also defines

which edge of the chosen clock to use to resynchronize the

captured data. If you select falling edge, the data path

automatically inserts inverters on the clock inputs to the

resynchronization registers.

When the resynchronization clock is set to either the system

clock or the write clock, you cannot alter the phase of the

resynchronization clock. To alter the resynchronization phase

clock, select the resynchronization clock as dedicated and

set the required phase.