Embedded displayport (edp), Signal definitions – Kontron COMe Starterkit Eval T2 User Manual

Page 99

COM Express Interfaces

2.12.

Embedded DisplayPort (eDP)

Embedded DisplayPort (eDP) is a digital display interface standard produced by the Video

Electronics Standards Association (VESA) for digital interconnect of Audio and Video.

Embedded DisplayPort defines a standardized display panel interface for internal connections;

e.g., graphics interfaces to notebook display panels. It supports advanced power-saving features

including seamless refresh rate switching, display panel and backlight control protocol that works

through the AUX channel, and Panel Self-Refresh (PSR) feature developed to save system

power and further extend battery life in portable PC systems. PSR mode allows the GPU to

enter power saving states in between frame updates by including framebuffer memory in the

display panel controller.

Embedded DisplayPort is intended to replace LVDS as the interface to flat panel displays

integrated into a product. Unlike DisplayPort, embedded DisplayPort does not define a specific

connector or pin-out. The COM Express specification shares the LVDS pins with embedded

DisplayPort.

2.12.1.

Signal Definitions

eDP is available in Type 6 and type 10 pin-outs as an alternative to the LVDS A channel. The

Module can provide LVDS only, eDP only or Dual-Mode for both interfaces. Please refer to

relevant Module documentation for the supported interfaces.

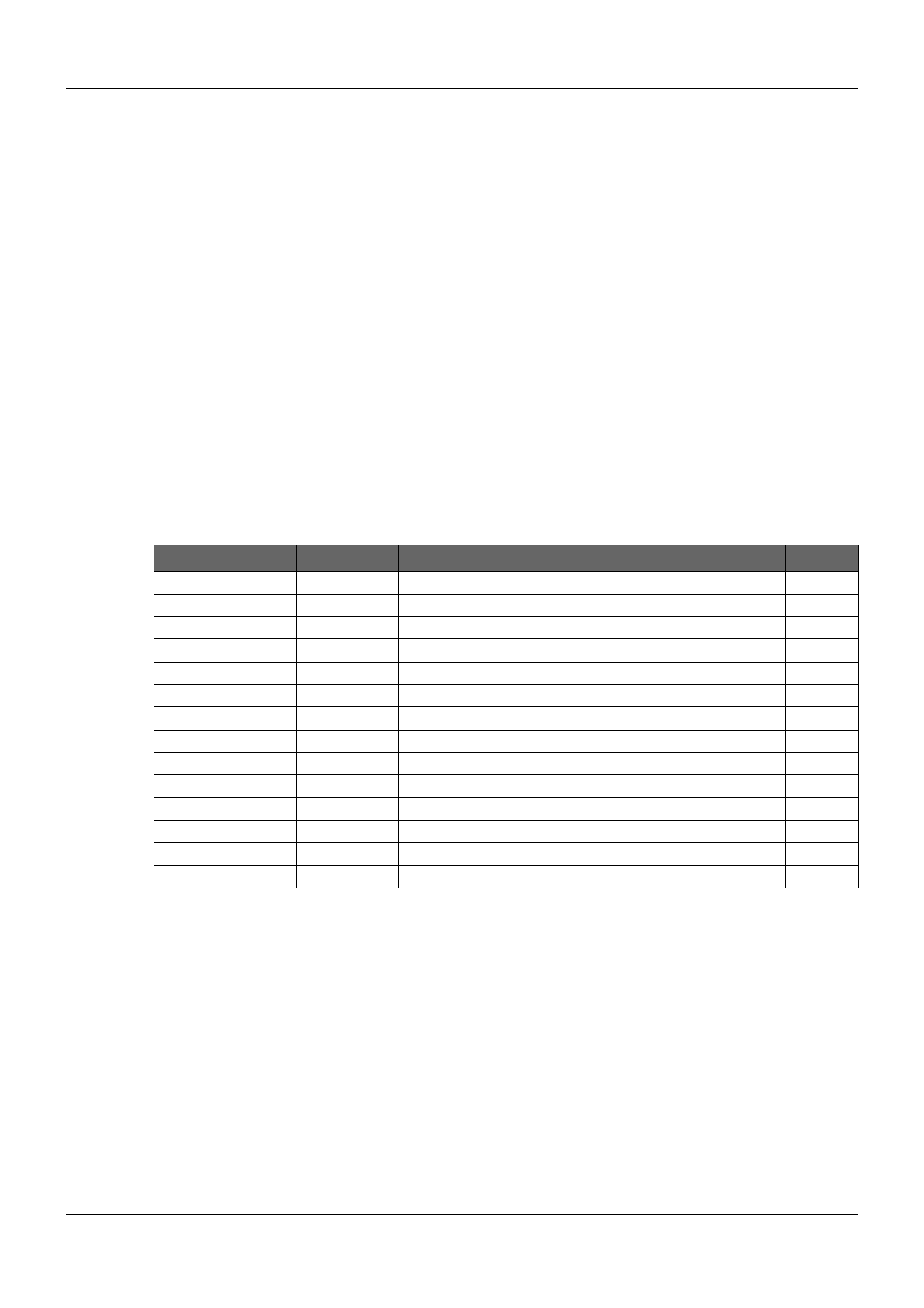

Table 31:

eDP Signal Description

Signal

Pins T6/T10 Description

I/O

eDP_TX0+

A75

eDP lane 0, TX +

O PCIe

eDP_TX0-

A76

eDP lane 0, TX -

O PCIe

eDP_TX1+

A73

eDP lane 1, TX +

O PCIe

eDP_TX1-

A74

eDP lane 1, TX -

O PCIe

eDP_TX2+

A71

eDP lane 2, TX +

O PCIe

eDP_TX2-

A72

eDP lane 2, TX -

O PCIe

eDP_TX3+

A81

eDP lane 3, TX +

O PCIe

eDP_TX3-

A82

eDP lane 3, TX -

O PCIe

eDP_VDD_EN

A77

eDP power enable

O CMOS

eDP_BLKT_EN

B79

eDP backlight enable

O CMOS

eDP_BLKT_CTRL

B83

EDP backlight brightness control

O CMOS

eDP_AUX+

A83

eDP auxiliary lane +

I/O PCIe

eDP_AUX-

A84

eDP auxiliary lane -

I/O PCIe

eDP_HPD

A87

Detection of Hot Plug / Unplug and notification of the link layer

I CMOS

PICMG

®

COM Express

®

Carrier Board Design Guide

Rev. 2.0 / December 6, 2013

99/218