Lvds, Signal definitions – Kontron COMe Starterkit Eval T2 User Manual

Page 91

COM Express Interfaces

2.11.

LVDS

2.11.1.

Signal Definitions

The COM Express Specification provides an optional LVDS interface on the COM Express A-B

connector. Module pins for two LVDS channels are defined and designated as LVDS_A and

LVDS_B.

Systems use a single-channel LVDS for most displays. Dual LVDS channels are used for very

high-bandwidth displays. Single-channel LVDS means that one complete RGB pixel is

transmitted per display input clock (also known as the shift clock – see Table 27 'LVDS Signal

Descriptions' below for a summary of LVDS terms). Dual-channel LVDS means that two

complete RGB pixels are transmitted per display input clock. The two pixels are adjacent along a

display line. Dual-channel LVDS does not mean that two LVDS displays can be driven.

Each COM Express LVDS channel consists of four differential data pairs and a differential clock

pair for a total of five differential pairs per channel. COM Express Modules and Module chipsets

may not use all pairs. For example, with 18-bit TFT displays, only three of the four data pairs on

the LVDS_A channel are used, along with the LVDS_A clock. The LVDS_B lines are not used.

The manner in which RGB data is packed onto the LVDS pairs (including packing order and color

depth) is not specified by the COM Express Specification. This may be Module-dependent.

Further mapping details are given in Section 2.11.1.6. 'LVDS Display Color Mapping Tables'

below.

There are five single-ended signals included to support the LVDS interface: two lines are used for

an I2C interface that may be used to support EDID or other panel information and identification

schemes. Additionally, there are an LVDS power enable (LVDS_VDD_EN) and backlight control

and enable lines (LVDS_BKLT_CTRL and LVDS_BKLT_EN).

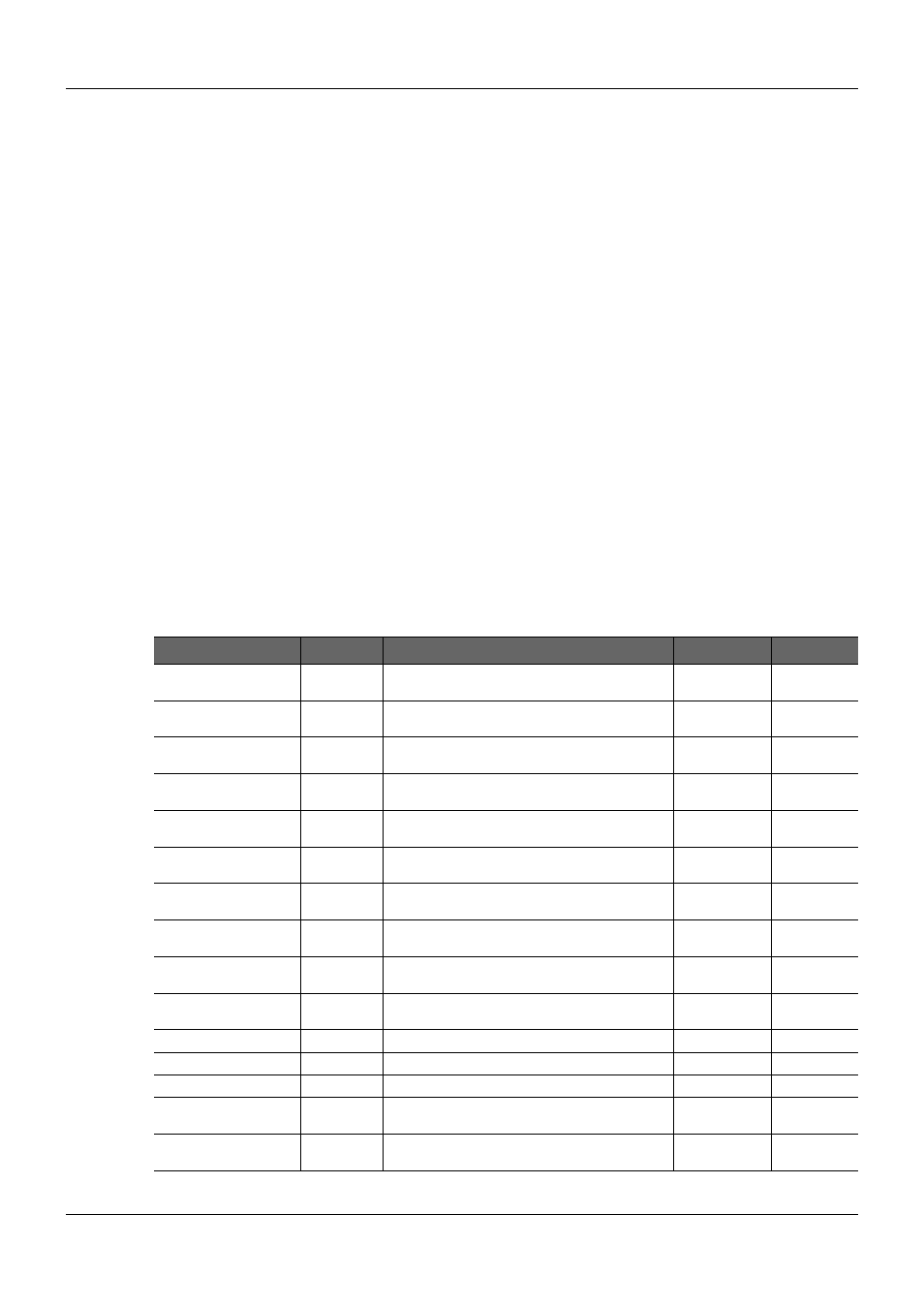

Table 27:

LVDS Signal Descriptions

Signal

Pin

Description

I/O

Comment

LVDS_A0+

LVDS_A0-

A71

A72

LVDS channel A differential signal pair 0

O LVDS

LVDS_A1+

LVDS_A1-

A73

A74

LVDS channel A differential signal pair 1

O LVDS

LVDS_A2+

LVDS_A2-

A75

A76

LVDS channel A differential signal pair 2

O LVDS

LVDS_A3+

LVDS_A3-

A78

A79

LVDS channel A differential signal pair 3

O LVDS

LVDS_A_CK+

LVDS_A_CK-

A81

A82

LVDS channel A differential clock pair

O LVDS

LVDS_B0+

LVDS_B0-

B71

B72

LVDS channel B differential signal pair 0

O LVDS

LVDS_B1+

LVDS_B1-

B73

B74

LVDS channel B differential signal pair 1

O LVDS

LVDS_B2+

LVDS_B2-

B75

B76

LVDS channel B differential signal pair 2

O LVDS

LVDS_B3+

LVDS_B3-

B77

B78

LVDS channel B differential signal pair 3

O LVDS

LVDS_B_CK+

LVDS_B_CK-

B81

B82

LVDS channel B differential clock pair

O LVDS

LVDS_VDD_EN

A77

LVDS flat panel power enable.

O 3.3V, CMOS

LVDS_BKLT_EN

B79

LVDS flat panel backlight enable high active signal O 3.3V, CMOS

LVDS_BKLT_CTRL

B83

LVDS flat panel backlight brightness control

O 3.3V, CMOS

LVDS_I2C_CK

A83

DDC I2C clock signal used for flat panel detection

and control.

O 3.3V, CMOS

LVDS_I2C_DAT

A84

DDC I2C data signal used for flat panel detection

and control.

I/O 3.3V,

OD CMOS

PICMG

®

COM Express

®

Carrier Board Design Guide

Rev. 2.0 / December 6, 2013

91/218