Reference schematic, Displayport example, Com express interfaces – Kontron COMe Starterkit Eval T2 User Manual

Page 56: Picmg, Com express

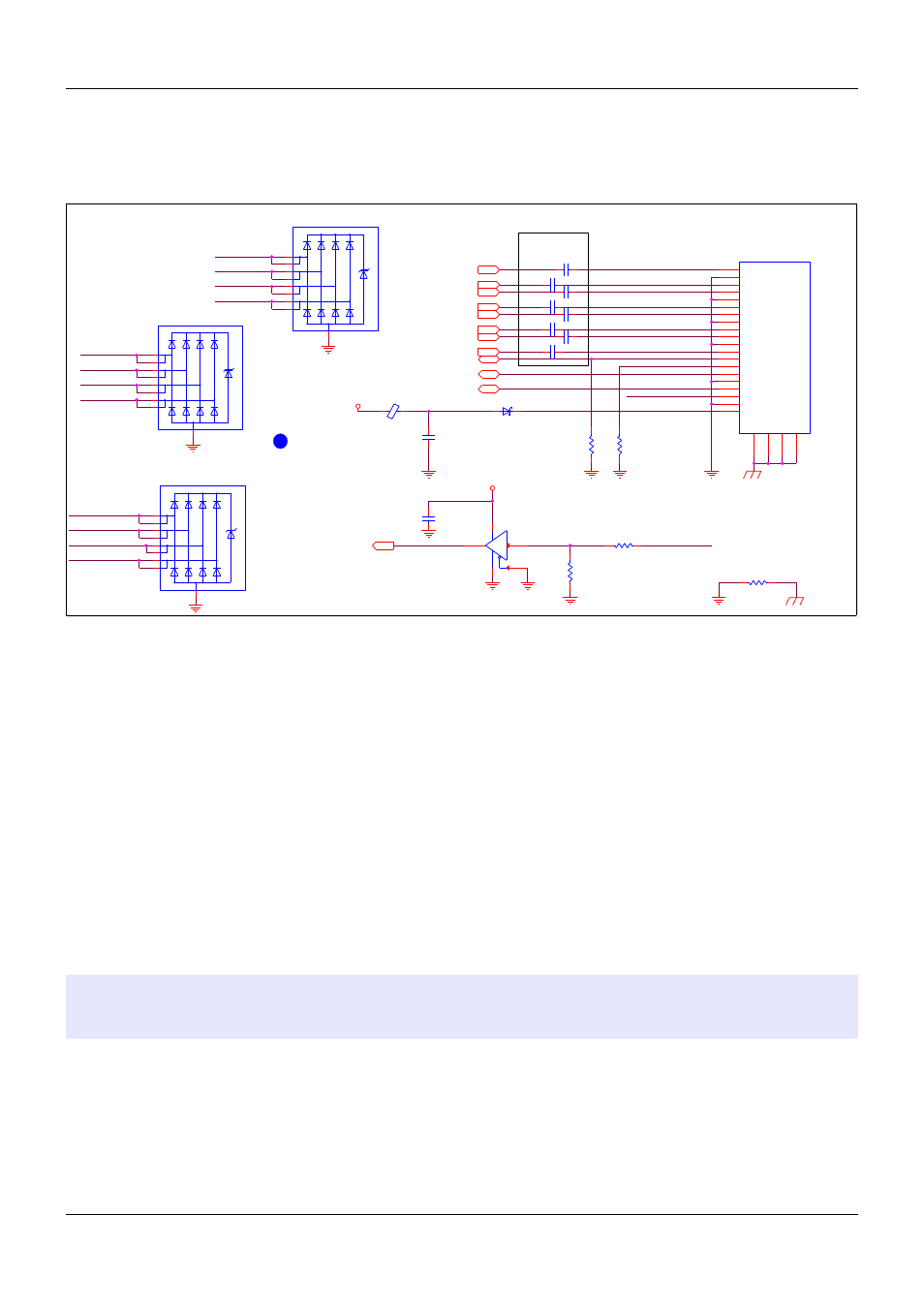

COM Express Interfaces

2.5.1.2.

Reference Schematic

DisplayPort Example

Figure 20:

DisplayPort Reference Schematics

DisplayPort is directly supported by a dual-source DDI. ESD protection, DC blocking capacitors

and hot plug detect are the only components required.

The DisplayPort differential data pairs (Lane [0..3]) are AC coupled off Module with capacitors

C19-C26. Place the AC blocking capacitors close to the DisplayPort connector. The Aux

differential pair is AC coupled on the Module. ESD clamping diodes D1, D2 and D3 protect the

Module from external ESD events and should be placed near the DisplayPort connector. The

pin-out of the ESD clamp diodes allows for a trace to run under the chip connector to two pins.

The Carrier provides up to 500 mA of 3.3V power to the DisplayPort connector. Diode D71

prevents back feeding of power in the event that the monitor is powered up when the Carrier is

powered down.

Config lines 1 and 2 are pulled to ground per the VESA specification.

The DisplayPort Hot Plug Detect signal is buffered by U50 which prevents back feeding of power

from the display to the Module as well as level translation to 3.3V levels.

R14 connect logic and chassis ground together. Other techniques may be used depending on

the overall grounding strategy.

Note:

The reference schematics assume that the Module’s DDI ports are dual-source

capable – dual source indicates that the Module can output DisplayPort or

HDMI/DVI based on the DDC_AUX_SEL signal.

PICMG

®

COM Express

®

Carrier Board Design Guide

Rev. 2.0 / December 6, 2013

56/218

i

m a x. 5 0 0 m A

0.5A

D D I3_H P D _C

V 3.3_S 0_D P _3

D D I3_ P A IR 1_ C -

V 3.3_S 0_D P _3

D D I3_P A IR 0_C +

D D I3_P A IR 0_C -

D D I3_C onfig2

D D I3_P A IR 1_C +

D D I3_P A IR 1_C -

D D I3_P A IR 2_C +

D D I3_P A IR 2_C -

D D I3_ P A IR 1_ C +

D D I3_P A IR 3_C +

D D I3 _ P A IR 3 _C -

D D I3 _ P A IR 3 _C +

D D I3 _ P A IR 2 _C -

D D I3 _ P A IR 2 _C +

D D I3_P A IR 3_C -

D D I3_ P A IR 0_ C -

D D I3_ P A IR 0_ C +

D D I3_H P D _C

D D I3_H P D _C

D D I3_C T R LD A T A _A U X -

D D I3_C T R LC LK _A U X +

D D I3_H P D _B

VCC_3V3

VCC_3V3

C E X

D D I3_P A IR 0+

C E X

D D I3_P A IR 0-

C E X

D D I3_P A IR 1+

C E X

D D I3_P A IR 1-

C E X

D D I3_P A IR 2+

C E X

D D I3_P A IR 2-

C E X

D D I3_P A IR 3+

C E X

D D I3_P A IR 3-

C E X

D D I3_H P D

C E X

D D I3_D D C _A U X _S E L

C E X

D D I3_C T R LC LK _A U X +

C E X

D D I3_C T R LD A T A _A U X -

U 50

N C 7S Z 125

1

2

3

4

5

R 16

1M

1%

C 2 4

1 0 0 n

10 %

5 0 V

J 3

M o le x 4 7 2 72 -0 0 0 1

M L_Lane0+

G N D

M L_Lane0-

M L_Lane1+

G N D

M L_Lane1-

M L_Lane2+

G N D

M L_Lane2-

M L_Lane3+

G N D

M L_Lane3-

C onfig1

C onfig2

A U X C H +

G N D

A U X C H -

H ot P lug

R eturn

D P _P W R

S

1

S

1

S

2

S

2

S

3

S

3

S

4

S

4

R 32

0R

5%

C25

D 71

M B R 130LS F T 1

C 2 1

R 15

5M 1

F B 4

60R @ 100M H z

C26

R 46

100k

1%

D 1

R clam p 0 5 2 4 P

5

1

4

2

9

3

10

7

6

C 2 3

R 14

0R

5%

D 2

R cla m p 0 5 2 4P

5

1

4

2

9

3

10

7

6

C 2 0

C 1 9

C 2 2

D 3

R cla m p 0 5 2 4P

5

1

4

2

9

3

10

7

6

C 305

10n

C 6

100n

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20