General purpose pcie lanes, General purpose pcie signal definitions – Kontron COMe Starterkit Eval T2 User Manual

Page 31

COM Express Interfaces

2.3.

General Purpose PCIe Lanes

2.3.1.

General Purpose PCIe Signal Definitions

The general purpose PCI Express interface of the COM Express Type 6 Module on the COM

Express A-B connector consists of up to 6 lanes plus 2 lanes on connector C-D, each with a

receive and transmit differential signal pair designated from PCIE_RX0 (+ and -) to PCIE_RX7 (+

and -) and correspondingly from PCIE_TX0 (+ and -) to PCIE_TX7 (+ and -). The 8 lanes may be

grouped into various link widths as defined in the COM Express spec and summarized in

Sections 2.3.3 and 2.3.2 below. The signals used are summarized in Table 6 below.

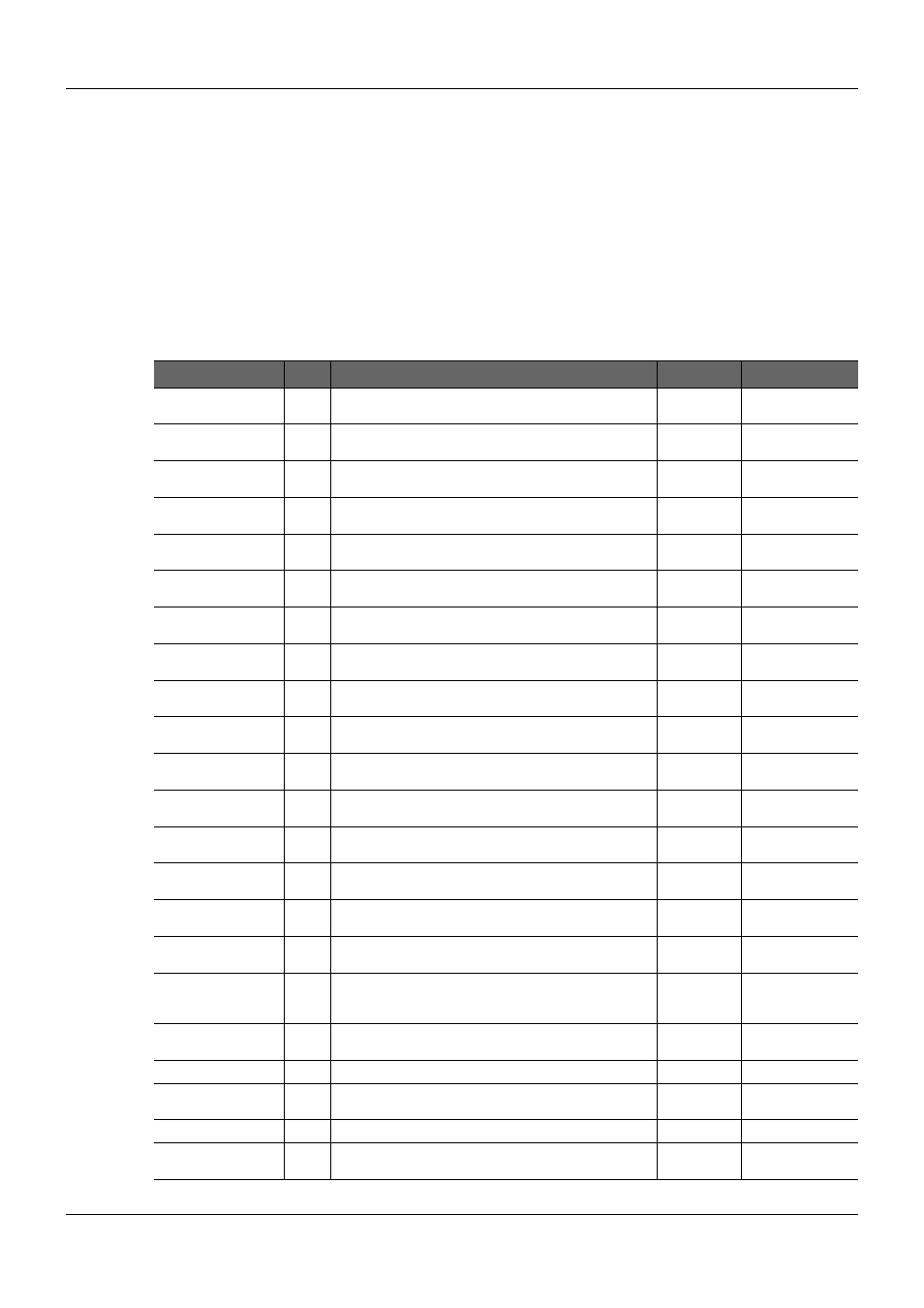

Table 6:

General Purpose PCI Express Signal Descriptions

Signal

Pin# Description

I/O

Comment

PCIE_RX0+

PCIE_RX0-

B68

B69

PCIe channel 0. Receive Input differential pair.

I PCIE

PCIE_TX0+

PCIE_TX0-

A68

A69

PCIe channel 0. Transmit Output differential pair.

O PCIE

PCIE_RX1+

PCIE_RX1-

B64

B65

PCIe channel 1. Receive Input differential pair.

I PCIE

PCIE_TX1+

PCIE_TX1-

A64

A65

PCIe channel 1. Transmit Output differential pair.

O PCIE

PCIE_RX2+

PCIE_RX2-

B61

B62

PCIe channel 2. Receive Input differential pair.

I PCIE

PCIE_TX2+

PCIE_TX2-

A61

A62

PCIe channel 2. Transmit Output differential pair.

O PCIE

PCIE_RX3+

PCIE_RX3-

B58

B59

PCIe channel 3. Receive Input differential pair.

I PCIE

PCIE_TX3+

PCIE_TX3-

A58

A59

PCIe channel 3. Transmit Output differential pair.

O PCIE

PCIE_RX4+

PCIE_RX4-

B55

B56

PCIe channel 4. Receive Input differential pair.

I PCIE

PCIE_TX4+

PCIE_TX4-

A55

A56

PCIe channel 4. Transmit Output differential pair.

O PCIE

PCIE_RX5+

PCIE_RX5-

B52

B53

PCIe channel 5. Receive Input differential pair.

I PCIE

PCIE_TX5+

PCIE_TX5-

A52

A53

PCIe channel 5. Transmit Output differential pair.

O PCIE

PCIE_RX6+

PCIE_RX6-

C19

C20

PCIe channel 6. Receive Input differential pair.

I PCIE

Type 6 only

PCIE_TX6+

PCIE_TX6-

D19

D20

PCIe channel 6. Transmit Output differential pair.

O PCIE

Type 6 only

PCIE_RX7+

PCIE_RX7-

C22

C23

PCIe channel 7. Receive Input differential pair.

I PCIE

Type 6 only

PCIE_TX7+

PCIE_TX7-

D22

D23

PCIe channel 7. Transmit Output differential pair.

O PCIE

Type 6 only

PCIE_CLK_REF+

PCIE_CLK_REF-

A88

A89

PCIe Reference Clock

for all COM Express PCIe lanes,

and for PEG lanes.

O PCIE

COM Express only

allocates a single

ref clock

EXCD0_CPPE#

A49

PCI ExpressCard0: PCI Express capable card request,

active low, one per card

I CMOS

EXCD0_PERST#

A48

PCI ExpressCard0: reset, active low, one per card

O CMOS

EXCD1_CPPE#

B48

PCI ExpressCard1: PCI Express capable card request,

active low, one per card

I CMOS

EXCD1_PERST#

B47

PCI ExpressCard1: reset, active low, one per card

O CMOS

CB_RESET#

B50

Reset output from Module to Carrier Board. Active low.

Issued by Module chipset and may result from a low

O CMOS

PICMG

®

COM Express

®

Carrier Board Design Guide

Rev. 2.0 / December 6, 2013

31/218