Peg (pci express graphics), Signal definitions, 'peg (pci express graphics) – Kontron COMe Starterkit Eval T2 User Manual

Page 48

COM Express Interfaces

2.4.

PEG (PCI Express Graphics)

2.4.1.

Signal Definitions

The PEG Port can utilize COM Express PCIe lanes 16-31 and is suitable to drive a link for an external

high-performance PCI Express Graphics card, if implemented on the COM Express Module.

Graphics Cards implemented as x16 use COM Express PCIe lanes 16-31; Graphics Cards

implemented as x8 lanes should use COM Express PCIe lanes 16-23. Each lane of the PEG Port

consists of a receive and transmit differential signal pair designated 'PEG_RX0' (+ and -) to

'PEG_RX15' (+ and -) and correspondingly from 'PEG_TX0' (+ and -) to 'PEG_TX15' (+ and -). The

corresponding signals can be found on the Module connector rows C and D.

On Type 2 Modules the pins of the PEG Port might be shared with other functionality like SDVO

or DVO, depending on the chipset used. SDVO and PEG are defined on COM Express

specification for Type 2 Modules as “may be used”. Please be sure the functionality you require

is supported by your Module vendor.

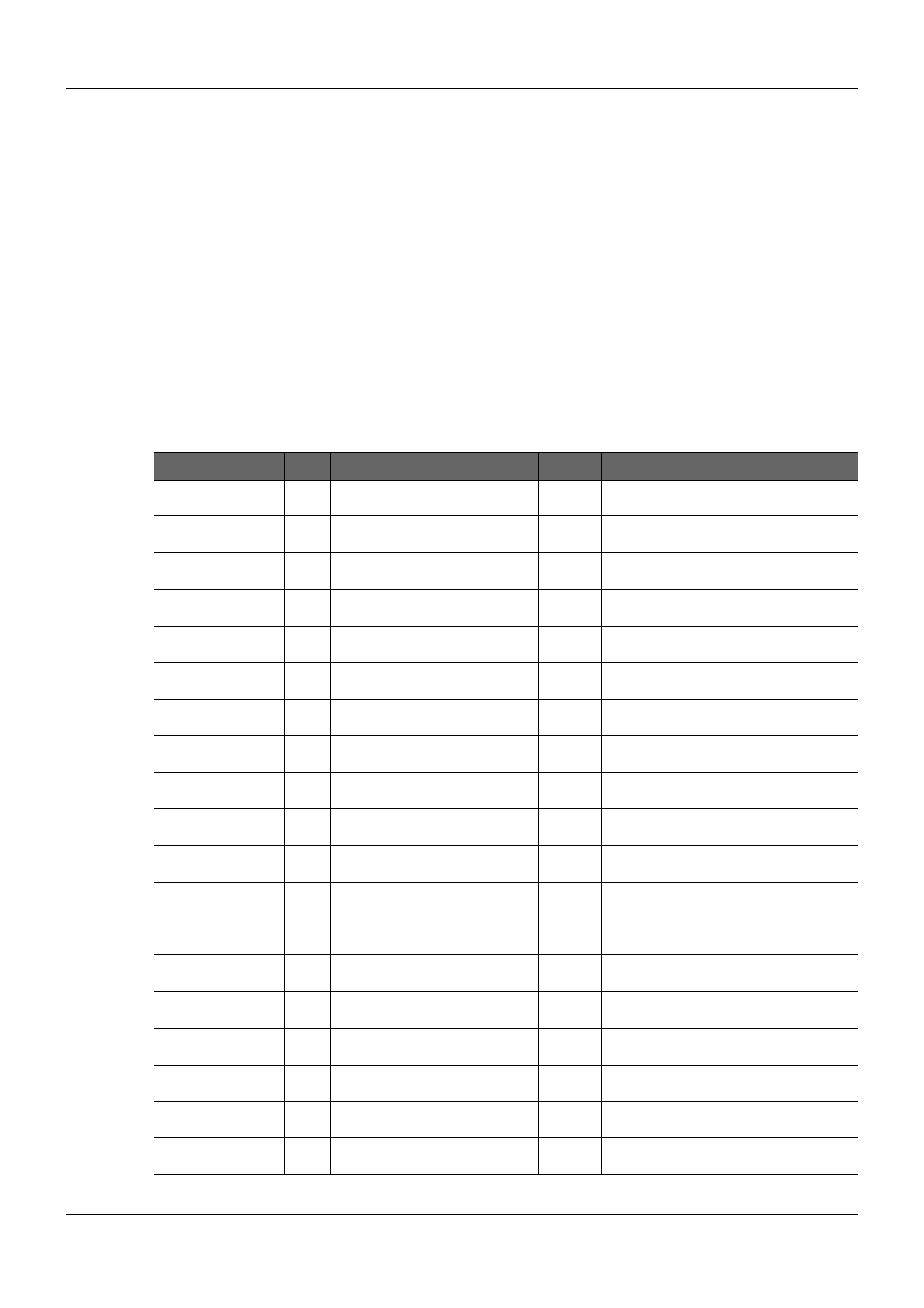

Table 9:

PEG Signal Description

Signal

Pin# Description

I/O

Comment

PEG_RX0+

PEG_RX0-

C52

C53

PEG channel 0, Receive Input

differential pair.

I PCIE

Type 2

SDVO_TVCLKIN+

Shared with:

SDVO_TVCLKIN-

PEG_TX0+

PEG_TX0-

D52

D53

PEG channel 0, Transmit Output

differential pair.

O PCIE

Type 2

SDVOB_RED+

Shared with:

SDVOB_RED-

PEG_RX1+

PEG_RX1-

C55

C56

PEG channel 1, Receive Input

differential pair.

I PCIE

Type 2

SDVOB_INT+

Shared with:

SDVOB_INT-

PEG_TX1+

PEG_TX1-

D55

D56

PEG channel 1, Transmit Output

differential pair.

O PCIE

Type 2

SDVOB_GRN+

Shared with:

SDVOB_GRN-

PEG_RX2+

PEG_RX2-

C58

C59

PEG channel 2, Receive Input

differential pair.

I PCIE

Type 2

SDVO_FLDSTALL+

Shared with:

SDVO_FLDSTALL-

PEG_TX2+

PEG_TX2-

D58

D59

PEG channel 2, Transmit Output

differential pair.

O PCIE

Type 2

SDVOB_BLU+

Shared with:

SDVOB_BLU-

PEG_RX3+

PEG_RX3-

C61

C62

PEG channel 3, Receive Input

differential pair.

I PCIE

PEG_TX3+

PEG_TX3-

D61

D62

PEG channel 3, Transmit Output

differential pair.

O PCIE

Type 2

SDVOB_CK+

Shared with:

SDVOB_CK-

PEG_RX4+

PEG_RX4-

C65

C66

PEG channel 4, Receive Input

differential pair.

I PCIE

PEG_TX4+

PEG_TX4-

D65

D66

PEG channel 4, Transmit Output

differential pair.

O PCIE

Type 2

SDVOC_RED+

Shared with:

SDVOC_RED-

PEG_RX5+

PEG_RX5-

C68

C69

PEG channel 5, Receive Input

differential pair.

I PCIE

Type 2

SDVOC_INT+

Shared with:

SDVOC_INT-

PEG_TX5+

PEG_TX5-

D68

D69

PEG channel 5, Transmit Output

differential pair.

O PCIE

Type 2

SDVOC_GRN+

Shared with:

SDVOC_GRN-

PEG_RX6+

PEG_RX6-

C71

C72

PEG channel 6, Receive Input

differential pair.

I PCIE

PEG_TX6+

PEG_TX6-

D71

D72

PEG channel 6, Transmit Output

differential pair.

O PCIE

Type 2

SDVOC_BLU+

Shared with

SDVOC_BLU-

PEG_RX7+

PEG_RX7-

C74

C75

PEG channel 7, Receive Input

differential pair.

I PCIE

PEG_TX7+

PEG_TX7-

D74

D75

PEG channel 7, Transmit Output

differential pair.

O PCIE

Type 2 :

SDVOC_CK+

Shared with

SDVOC_CK-

PEG_RX8+

PEG_RX8-

C78

C79

PEG channel 8, Receive Input

differential pair.

I PCIE

PEG_TX8+

PEG_TX8-

D78

D79

PEG channel 8, Transmit Output

differential pair.

O PCIE

PEG_RX9+

PEG_RX9-

C81

C82

PEG channel 9, Receive Input

differential pair.

I PCIE

PICMG

®

COM Express

®

Carrier Board Design Guide

Rev. 2.0 / December 6, 2013

48/218