Kontron COMe Starterkit Eval T2 User Manual

Page 32

COM Express Interfaces

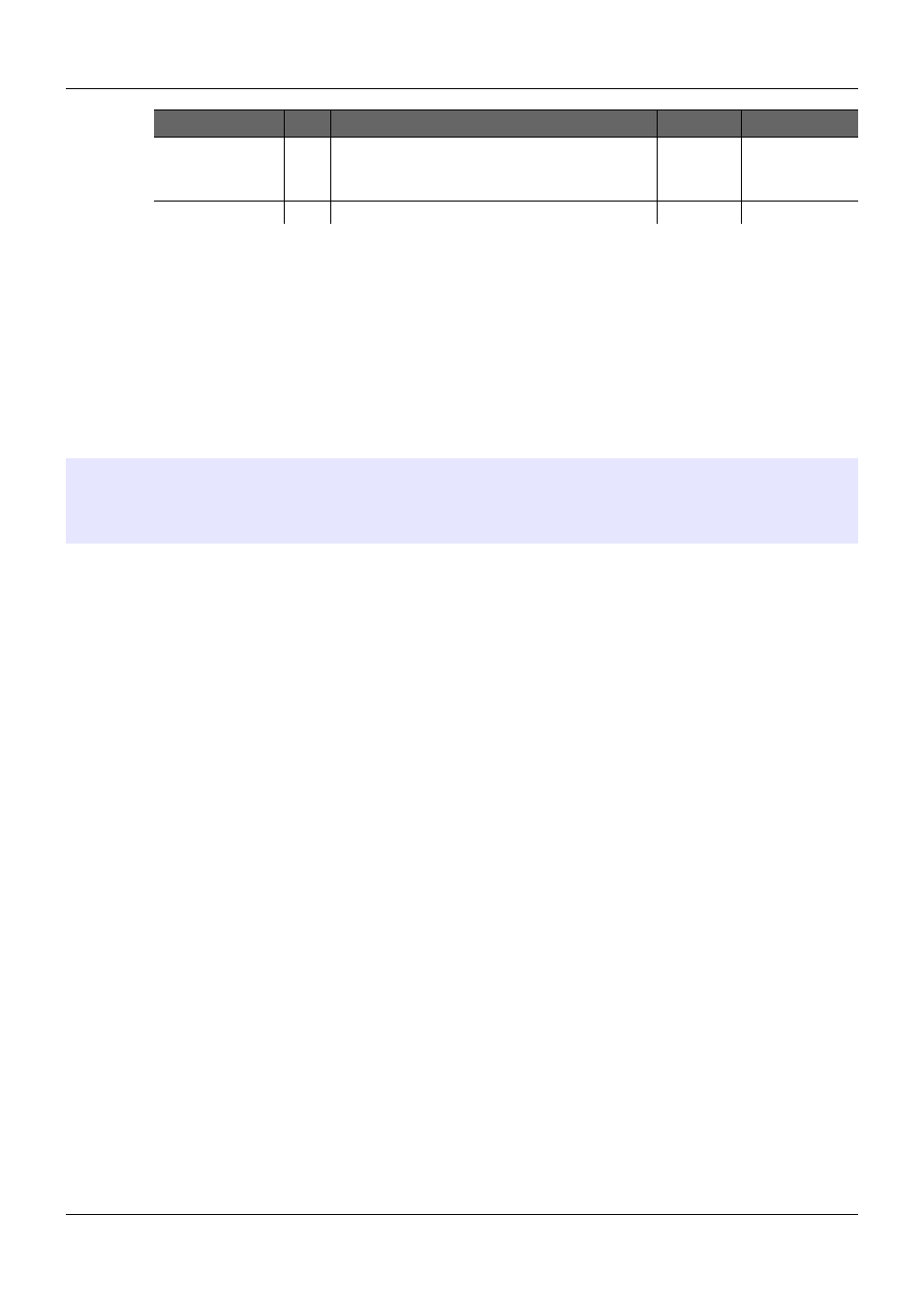

Signal

Pin# Description

I/O

Comment

SYS_RESET# input, a low PWR_OK input, a VCC_12V

power input that falls below the minimum specification, a

watchdog timeout, or may be initiated by the Module

software.

WAKE0#

B66

PCI Express wake up signal

I CMOS

2.3.2.

PCI Express Lane Configurations – Per COM Express Spec

According to the COM Express specification, the general purpose PCIe lanes on the A-B

connector can be configured as up to eight PCI Express x1 links or may be combined into

various combinations of x8, x4, x2 and x1 links that add up to a total of 8 lanes. These

configuration possibilities are based on the COM Express Module's chip-set capabilities.

The COM Express specification defines a "fill order" from mapping PCIe links that are wider than

x1 onto the COM Express pins. For example, the spec requires that a x4 PCI Express link be

mapped to COM Express PCI Express lanes 0,1,2 and 3. Refer to the COM Express

specification for details.

Note:

All PCI Express devices are required to work in x1 mode as well as at their full

capability

.

A x4 PCIe card for example is required by the PCI Express

specification to be usable in x4 and / or x1 mode

.

The "in-between" modes (x2

in this case) are optional.

2.3.3.

PCI Express Lane Configurations – Module and Chipset Dependencies

The lane configuration possibilities of the PCI Express interface of a COM Express Module are

dependent on the Module's chip-set. Some Module and chip-set implementations may allow

software or setup screen configuration of link width (x1, x2, x4, x8). Others may require a

hardware strap or build option on the Module to configure the x4 or x8 option. The COM Express

specification does not allocate any Module pins for strapping PCIe lane width options.

Refer to the vendor specific Module documentation for the Module that you are using for

additional information about this subject.

PICMG

®

COM Express

®

Carrier Board Design Guide

Rev. 2.0 / December 6, 2013

32/218