Kontron COMe Starterkit Eval T2 User Manual

Page 96

COM Express Interfaces

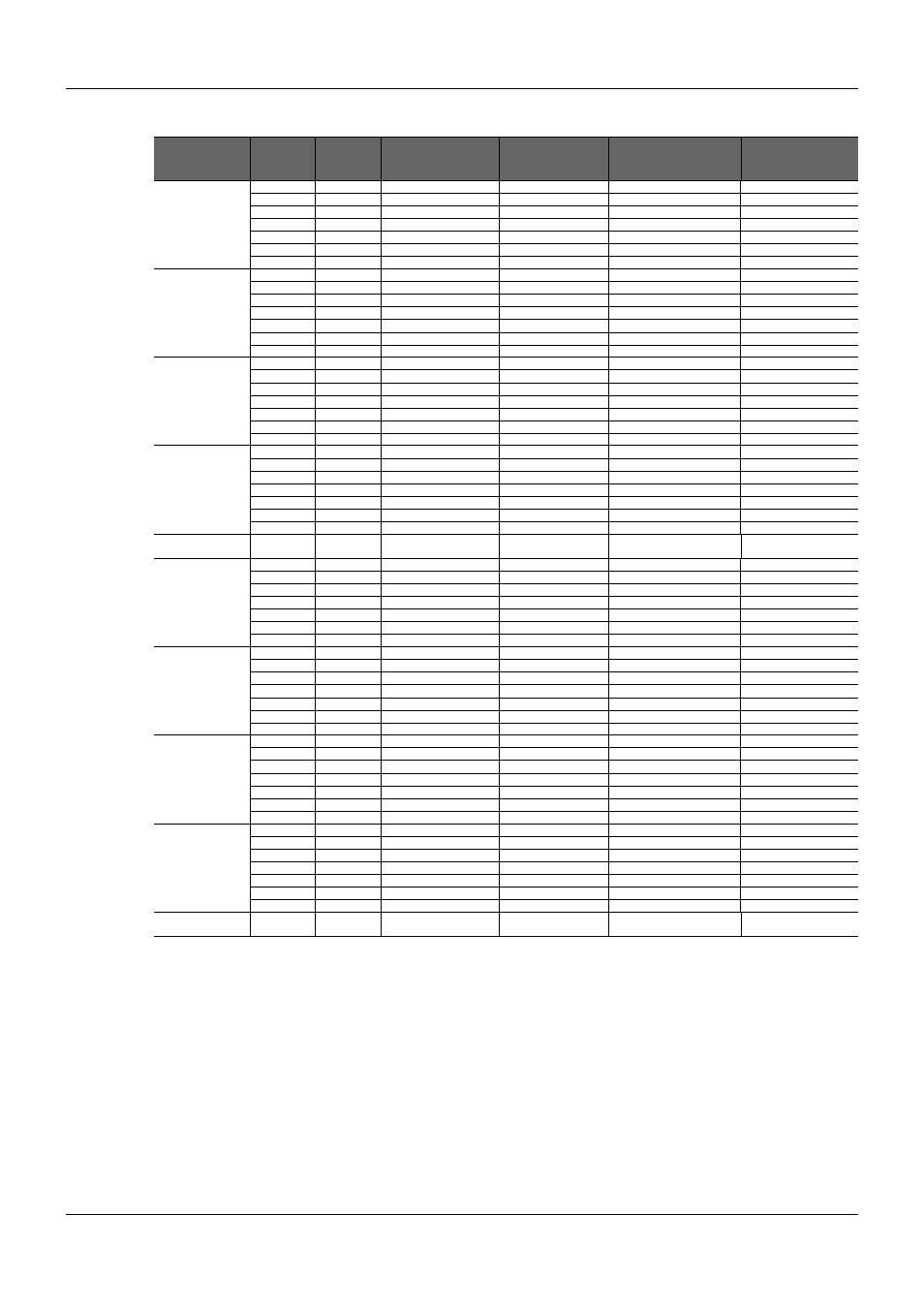

Table 30:

LVDS Display: Dual Channel, Unbalanced Color-Mapping

Xmit

Bit

Order

LVDS

Clock

Open LDI

18 bit (36 bit)

Dual Ch

Open LDI

24 bit (48 bit)

Dual Ch

FPD Link

18 bit (36 bit)

Dual Ch

FPD Link

24 bit (48 bit)

Dual Ch

LVDS_A0±

1

1

Odd Pixel G0

Odd Pixel G2

Odd Pixel G0

Odd Pixel G0

2

1

Odd Pixel R5

Odd Pixel R7

Odd Pixel R5

Odd Pixel R5

3

0

Odd Pixel R4

Odd Pixel R6

Odd Pixel R4

Odd Pixel R4

4

0

Odd Pixel R3

Odd Pixel R5

Odd Pixel R3

Odd Pixel R3

5

0

Odd Pixel R2

Odd Pixel R4

Odd Pixel R2

Odd Pixel R2

6

1

Odd Pixel R1

Odd Pixel R3

Odd Pixel R1

Odd Pixel R1

7

1

Odd Pixel R0

Odd Pixel R2

Odd Pixel R0

Odd Pixel R0

LVDS_A1±

1

1

Odd Pixel B1

Odd Pixel B3

Odd Pixel B1

Odd Pixel B1

2

1

Odd Pixel B0

Odd Pixel B2

Odd Pixel B0

Odd Pixel B0

3

0

Odd Pixel G5

Odd Pixel G7

Odd Pixel G5

Odd Pixel G5

4

0

Odd Pixel G4

Odd Pixel G6

Odd Pixel G4

Odd Pixel G4

5

0

Odd Pixel G3

Odd Pixel G5

Odd Pixel G3

Odd Pixel G3

6

1

Odd Pixel G2

Odd Pixel G4

Odd Pixel G2

Odd Pixel G2

7

1

Odd Pixel G1

Odd Pixel G3

Odd Pixel G1

Odd Pixel G1

LVDS_A2±

1

1

DE

DE

DE

DE

2

1

VSYNC

VSYNC

VSYNC

VSYNC

3

0

HSYNC

HSYNC

HSYNC

HSYNC

4

0

Odd Pixel B5

Odd Pixel B7

Odd Pixel B5

Odd Pixel B5

5

0

Odd Pixel B4

Odd Pixel B6

Odd Pixel B4

Odd Pixel B4

6

1

Odd Pixel B3

Odd Pixel B5

Odd Pixel B3

Odd Pixel B3

7

1

Odd Pixel B2

Odd Pixel B4

Odd Pixel B2

Odd Pixel B2

LVDS_A3±

1

1

2

1

Odd Pixel B1

Odd Pixel B7

3

0

Odd Pixel B0

Odd Pixel B6

4

0

Odd Pixel G1

Odd Pixel G7

5

0

Odd Pixel G0

Odd Pixel G6

6

1

Odd Pixel R1

Odd Pixel R7

7

1

Odd Pixel R0

Odd Pixel R6

LVDS_A_CK±

LCLK= PCLK / 14

SCLK = PCLK / 2

LCLK = PCLK / 14

SCLK = PCLK / 2

LCLK= PCLK / 14

SCLK = PCLK / 2

LCLK = PCLK / 14

SCLK = PCLK / 2

LVDS_B0±

1

1

Even Pixel G0

Even Pixel G2

Even Pixel G0

Even Pixel G0

2

1

Even Pixel R5

Even Pixel R7

Even Pixel R5

Even Pixel R5

3

0

Even Pixel R4

Even Pixel R6

Even Pixel R4

Even Pixel R4

4

0

Even Pixel R3

Even Pixel R5

Even Pixel R3

Even Pixel R3

5

0

Even Pixel R2

Even Pixel R4

Even Pixel R2

Even Pixel R2

6

1

Even Pixel R1

Even Pixel R3

Even Pixel R1

Even Pixel R1

7

1

Even Pixel R0

Even Pixel R2

Even Pixel R0

Even Pixel R0

LVDS_B1±

1

1

Even Pixel B1

Even Pixel B3

Even Pixel B1

Even Pixel B1

2

1

Even Pixel B0

Even Pixel B2

Even Pixel B0

Even Pixel B0

3

0

Even Pixel G5

Even Pixel G7

Even Pixel G5

Even Pixel G5

4

0

Even Pixel G4

Even Pixel G6

Even Pixel G4

Even Pixel G4

5

0

Even Pixel G3

Even Pixel G5

Even Pixel G3

Even Pixel G3

6

1

Even Pixel G2

Even Pixel G4

Even Pixel G2

Even Pixel G2

7

1

Even Pixel G1

Even Pixel G3

Even Pixel G1

Even Pixel G1

LVDS_B2±

1

1

2

1

3

0

4

0

Even Pixel B5

Even Pixel B7

Even Pixel B5

Even Pixel B5

5

0

Even Pixel B4

Even Pixel B6

Even Pixel B4

Even Pixel B4

6

1

Even Pixel B3

Even Pixel B5

Even Pixel B3

Even Pixel B3

7

1

Even Pixel B2

Even Pixel B4

Even Pixel B2

Even Pixel B2

LVDS_B3±

1

1

2

1

Even Pixel B1

Even Pixel B7

3

0

Even Pixel B0

Even Pixel B6

4

0

Even Pixel G1

Even Pixel G7

5

0

Even Pixel G0

Even Pixel G6

6

1

Even Pixel R1

Even Pixel R7

7

1

Even Pixel R0

Even Pixel R6

LVDS_B_CK±

LCLK= PCLK / 14

SCLK = PCLK / 2

LCLK = PCLK / 14

SCLK = PCLK / 2

LCLK= PCLK / 14

SCLK = PCLK / 2

LCLK = PCLK / 14

SCLK = PCLK / 2

PICMG

®

COM Express

®

Carrier Board Design Guide

Rev. 2.0 / December 6, 2013

96/218